The electron microscope is a powerful scientific instrument that revolutionized the field of materials science and biology by enabling the visualization and analysis of structures at the atomic and molecular level. This comprehensive guide will delve into the intricate details of electron microscopy, providing science students with a deep understanding of its principles, applications, and the latest advancements in this cutting-edge technology.

Understanding the Fundamentals of Electron Microscopy

Electron microscopes operate on the principle of using a beam of accelerated electrons, rather than light, to illuminate and interact with a sample. This approach allows for much higher resolution imaging compared to traditional optical microscopes, which are limited by the wavelength of visible light.

The key components of an electron microscope include:

-

Electron Gun: The electron gun is responsible for generating and accelerating the electron beam. It typically uses a tungsten filament or a field emission source to produce the electrons, which are then accelerated by a high voltage (typically ranging from 60 kV to 300 kV).

-

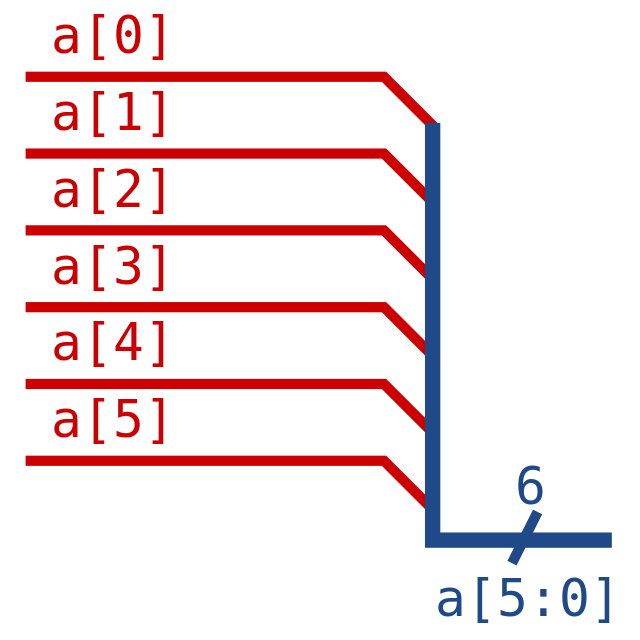

Electromagnetic Lenses: Electromagnetic lenses, similar to the glass lenses in optical microscopes, are used to focus and manipulate the electron beam. These lenses are composed of coils of wire that create a magnetic field, which can bend the path of the electrons.

-

Vacuum System: Electron microscopes require a high-vacuum environment to prevent the electron beam from being scattered by air molecules. This vacuum system ensures that the electrons can travel unimpeded from the electron gun to the sample and the detector.

-

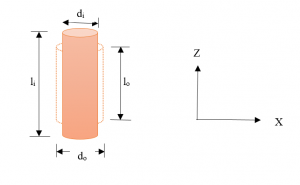

Sample Stage: The sample stage is where the specimen is placed for observation. It can be moved in three dimensions (x, y, and z) to allow for the examination of different areas of the sample.

-

Detector: The detector, such as a scintillator-photomultiplier tube or a charge-coupled device (CCD) camera, is responsible for converting the interactions between the electron beam and the sample into a signal that can be processed and displayed as an image.

Types of Electron Microscopes

There are several types of electron microscopes, each with its own unique capabilities and applications:

-

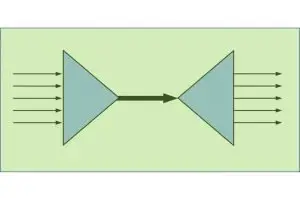

Transmission Electron Microscope (TEM): In a TEM, the electron beam passes through a thin specimen, and the transmitted or scattered electrons are detected to form an image. TEMs can achieve extremely high resolutions, down to the atomic scale, making them invaluable for studying the structure of materials and biological samples.

-

Scanning Electron Microscope (SEM): In an SEM, the electron beam scans the surface of a sample, and the secondary or backscattered electrons are detected to create a three-dimensional image of the sample’s topography. SEMs are widely used for surface analysis and characterization of materials.

-

Scanning Transmission Electron Microscope (STEM): STEM combines the principles of both TEM and SEM, where the electron beam is focused into a small spot and scanned across the sample. This allows for high-resolution imaging and the ability to perform analytical techniques, such as energy-dispersive X-ray spectroscopy (EDS), to determine the elemental composition of the sample.

-

Cryo-Electron Microscope (Cryo-EM): Cryo-EM is a specialized technique where the sample is cooled to cryogenic temperatures, typically using liquid nitrogen or liquid helium. This approach helps to preserve the native structure of biological samples, such as proteins and macromolecular complexes, allowing for high-resolution imaging and structural analysis.

Resolution and Image Quality in Electron Microscopy

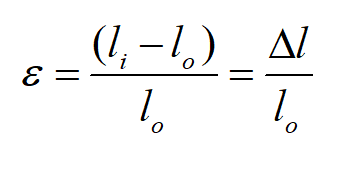

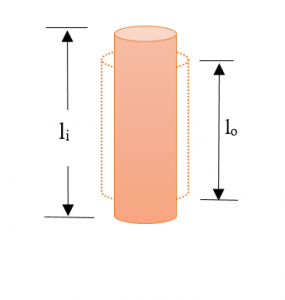

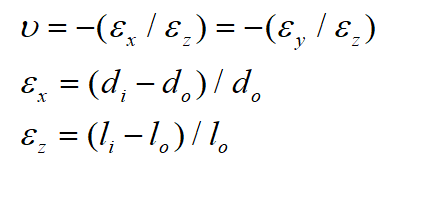

The resolution of an electron microscope is a critical factor in its performance, as it determines the level of detail that can be observed in the resulting image. The resolution of an electron microscope is typically measured in angstroms (Å) or nanometers (nm), with the best modern instruments capable of achieving sub-ångström resolution.

The factors that influence the resolution of an electron microscope include:

-

Electron Beam Energy: Higher electron beam energies (e.g., 200 kV or 300 kV) generally result in higher resolutions due to the shorter wavelength of the electrons.

-

Lens Aberrations: Imperfections in the electromagnetic lenses, such as spherical and chromatic aberrations, can limit the achievable resolution. Advances in lens design and aberration correction techniques have significantly improved the resolution of modern electron microscopes.

-

Specimen Preparation: The way the sample is prepared and mounted can also affect the resolution. Proper sample preparation techniques, such as thin sectioning, staining, and cryogenic freezing, are crucial for obtaining high-quality images.

-

Environmental Factors: Factors such as vibrations, electromagnetic interference, and thermal instability can degrade the resolution of an electron microscope. Careful control of the microscope’s environment is essential for achieving the best possible image quality.

To evaluate the quality and consistency of the results obtained from electron microscopy, various resolution measures are used, including:

-

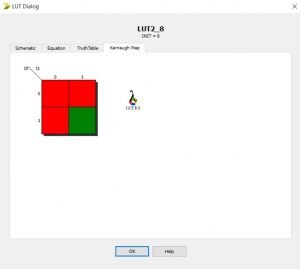

Fourier Ring Correlation (FRC): FRC is a widely used method that evaluates the correlation between two independent reconstructions of a macromolecular structure in the Fourier domain. It provides a quantitative assessment of the resolution and the signal-to-noise ratio (SNR) of the reconstruction.

-

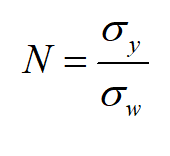

Q-factor: The Q-factor is a measure of the consistency between the experimental data and the computed density map. It is calculated as the ratio of the Fourier transform of the experimental data to the Fourier transform of the computed map, and it provides a measure of the overall quality of the reconstruction.

-

Differential Phase Residual (DPR): DPR is a resolution measure that evaluates the consistency of the phase information in the Fourier domain. It is particularly useful for assessing the resolution of cryo-EM reconstructions, where the phase information is crucial for determining the structure of macromolecular complexes.

These resolution measures are essential for understanding the quality and limitations of the data obtained from electron microscopy experiments, and they guide the optimization of the data processing and reconstruction algorithms.

Advances in Electron Microscopy Techniques

The field of electron microscopy is constantly evolving, with researchers and engineers continuously pushing the boundaries of what is possible. Some of the recent advancements in electron microscopy include:

-

Electron Counting Detectors: The development of electron counting detectors, such as direct electron detectors, has revolutionized the field of electron microscopy. These detectors can record individual electron events, leading to improved signal-to-noise ratios and enhanced image quality, particularly in low-dose imaging applications like cryo-EM.

-

Automated Data Processing: The increasing complexity of electron microscopy data has led to the development of automated data processing algorithms and software. These tools can streamline the analysis of large datasets, improve the consistency and reproducibility of results, and enable the extraction of more detailed information from the acquired images.

-

Machine Learning and Artificial Intelligence: The integration of machine learning and artificial intelligence (AI) techniques into electron microscopy has opened up new possibilities for image analysis, feature extraction, and even the enhancement of image resolution. These approaches can help to overcome the limitations of traditional image processing methods and unlock new insights from electron microscopy data.

-

In-situ and Operando Electron Microscopy: The ability to observe materials and processes in their native environments, or under operating conditions, has been a significant focus of recent advancements in electron microscopy. Techniques like in-situ heating, cooling, and gas/liquid flow cells allow researchers to study dynamic processes and the behavior of materials in real-time.

-

Correlative Microscopy: The combination of electron microscopy with other imaging techniques, such as light microscopy, X-ray microscopy, or atomic force microscopy, has led to the development of correlative microscopy approaches. These methods enable the integration of complementary information from multiple imaging modalities, providing a more comprehensive understanding of the sample under investigation.

-

Miniaturization and Democratization: Efforts are underway to develop more compact and affordable electron microscopes, making this powerful technology more accessible to a wider range of researchers, educators, and even citizen scientists. These advancements have the potential to democratize electron microscopy and expand its applications in various fields.

Conclusion

The electron microscope is a remarkable scientific instrument that has revolutionized our understanding of the microscopic world. This comprehensive guide has explored the fundamental principles, various types, and the critical factors that influence the resolution and image quality in electron microscopy. Additionally, it has highlighted the exciting advancements that are pushing the boundaries of this technology, from electron counting detectors to the integration of machine learning and artificial intelligence.

By understanding the intricacies of electron microscopy, science students can unlock a wealth of opportunities for cutting-edge research, materials characterization, and the exploration of the nanoscale universe. This guide serves as a valuable resource for those seeking to deepen their knowledge and expertise in this transformative field of scientific inquiry.

References:

- Pawel A. Penczek, “Resolution measures in molecular electron microscopy,” PMC3165049, 2010.

- Various authors, “Bringing into play automated electron microscopy data processing,” ScienceDirect, 2022.

- Various authors, “Electron counting detectors in scanning transmission electron microscopy,” Nature, 2023.

- Various authors, “Machine-learning approach for quantified resolvability enhancement in scanning transmission electron microscopy,” IOP Science, 2023.

- Various authors, “Reimagining electron microscopy: Bringing high-end resolution to lower-cost microscopes,” University of Illinois Urbana-Champaign, 2024.