VLSI, VHDL, Verilog Interview Questions

1. Give the full term of VHDL.

- Very High Definition Language

- Very High Speed Integration Hardware Description Language

- Very High Description Language

- Very High Speed Scaling Hardware Describing Language

Ans: 2) Very High Speed Integration Hardware Description Language

For basic VHDL Tutorials, Click Here!

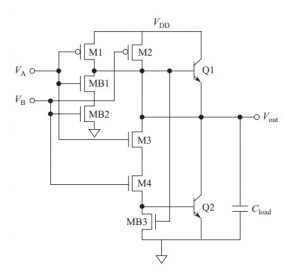

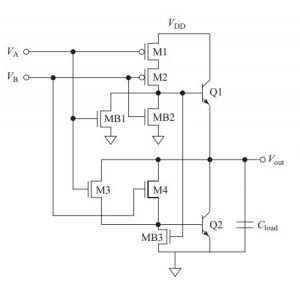

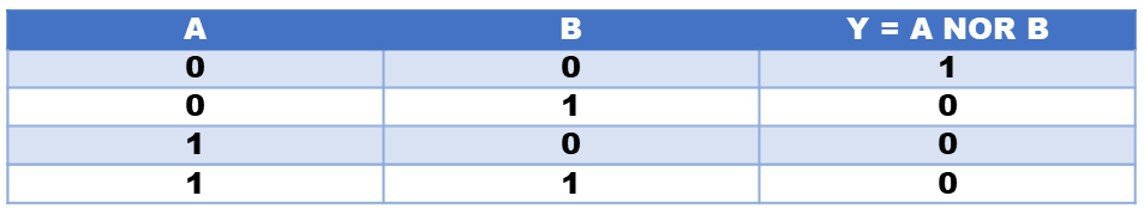

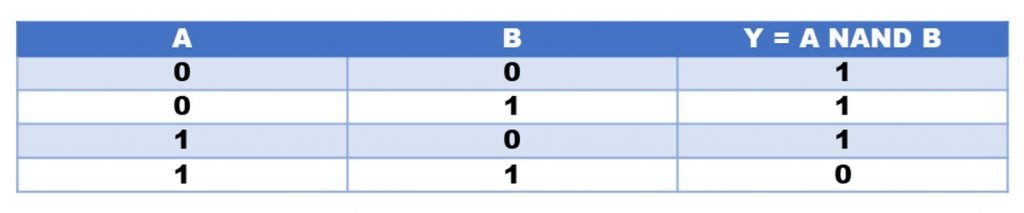

2. What is the number of Metal Oxide Filed Effect Transistors are needed to construct a Bi-complementary metal Oxide Semiconductor NOR gate which have two input?

- 5 MOSFETs

- 6 MOSFETs

- 7 MOSFETs

- 8 MOSFETs

Ans: 3) 7 MOSFETs

“How a Logic gate is designed in VLSI?” Find the answer here!

3. What is the effect of ‘Delay’ if the power supply voltage gets increased?

- Increases

- Decreases

- Remains the same

- Delay has nothing o do with power supply.

Ans: 2) Decreases

4. Which is true about VLSI design?

- VLSI is a sequential process which has feedback loops.

- VLSI is a parallel process which has no feedback loops.

- VLSI is both sequential and parallel process that has feedback loops.

- VLSI is a sequential process which has no feedback loops.

Ans: 3) VLSI is both sequential and parallel process that has feedback loops.

For more details about Verilog Interview Questions and other topic like VLSI Design, Check this!

5. What is the use of CAD tools in VLSI design?

- It automates the VLSI design.

- It reduces the design cycle time.

- It reduces the chance of errors.

- All of the above.

Ans: 4) All of the above.

6. Which type of product is more suitable for FPGA based Design?

- Large scale product development.

- High Speed applications.

- Prototype development.

- Low power applications.

Ans: 3) Prototype development.

What is Verilog? What is system Verilog? and other Verilog Interview Questions and Answers are here!

7. What is the relation between interconnect delay and gate delay?

- The Relation is technology dependent.

- Gate delay always more than interconnect delay.

- Interconnect delay always more than the gate delay.

- They are same.

Ans: 1) The relation is technology dependent.

8. State True or False

Statement: For a Y chart, the details of design information increases when moved from the centre to the periphery.

- True

- False

Ans: (2). False

9. Why a short channel device is preferred?

- It is easier for fabrication.

- It has lower power consumption.

- It has high speed.

- It has better output characteristics.

Ans: 3) It has high speed.

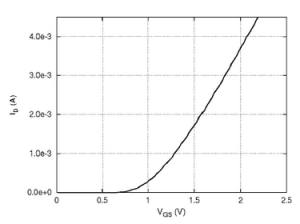

10. Where does the subthreshold operation of MOSFET find applications?

- Memories.

- Charge coupled devices.

- Biomedical applications.

- None of the above.

Ans: 3) Biomedical applications.

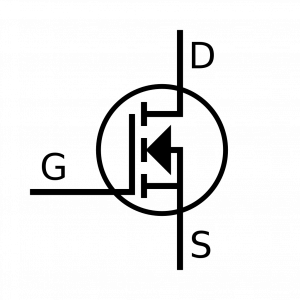

11. What is the relation between the ON-resistance of MOSFET and gate to source voltage (Vgs)?

- ON-resistance linearly increases with Vgs.

- ON-resistance linearly decreases with Vgs.

- ON-resistance exponentially increases with Vgs.

- ON-resistance non-linearly decreases with Vgs.

Ans: 4) ON-resistance non-linearly decreases with Vgs.

12. What is the threshold voltage of an EMOSFET?

- Equal to 0 V.

- Less than 0 V.

- Greater than 0 V.

- None of the above.

Ans: 3) Greater than 0 V.

13. Find the odd one out.

- Channel length modulation

- Subthreshold Conduction

- Hot carrier effect.

- Body Effect

Ans: 4) Body effect. (All the other options are 2nd order effect).

14. How does doping density change for constant voltage scaling?

- Increases by a factor of s

- Increases by a factor of s2.

- Decreases by a factor for s.

- Decreases by a factor for s2.

Ans: 2) Increases by a factor of s2.

15. How does power dissipation occur for full scaling?

- Increases by a factor of s

- Increases by a factor of s2.

- Decreases by a factor for s.

- Decreases by a factor for s2.

Ans: 3) Decreases by a factor of s2.

16. How does power dissipation occur for constant voltage scaling?

- Increases by a factor of s

- Increases by a factor of s2.

- Decreases by a factor for s.

- Decreases by a factor for s2.

Ans: 1) Increases by a factor of s.

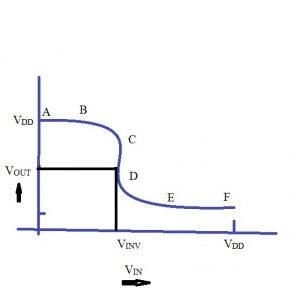

17. What is the main advantage of depletion load NMOSFET inverter over EMOSFET load?

- Less power dissipation

- Easier fabrication process

- Sharper Vtc transitions and better noise margins.

- None of the above.

Ans: 3) Sharper Vtc transitions and better noise margin.

18. Why is polysilicon used for the gate in MOSFET?

- Because it is a semi-metal.

- Because it has lattice matching with Silicone

- Because it is easier to fabricate.

- None of the above.

Ans: 2) Because it has lattice matching with silicone.

19. State True or False

Statement: In full scaling, the magnitude of the electric field is constant.

- True

- False

Solution: (1). True

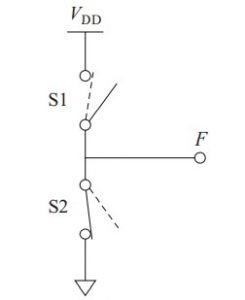

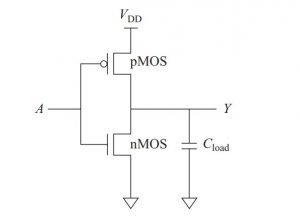

20. Which of the given statement is true regarding a MOSFET inverter?

- One PMOSFET and one resistor are needed to implement a MOSFET inverter.

- One NMOSFET and one resistor are needed to implement a MOSFET inverter.

- Two PMOSFETs.

- Two NMOSFETs.

Ans: 2) One NMOSFET and one resistor is needed to implement a MOSFET inverter.

21. On which factors, the power dissipation of a CMOS inverter depends?

- Supplied Voltage.

- NMOSFET’s channel width.

- PMOSFET’s channel width.

- All of the above.

Ans: 1) Supplied Voltage

22. State True or False

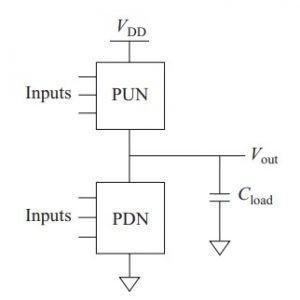

Statement: The PMOS transistors act as Pull-up network in a CMOS inverter.

- True

- False

Solution: (1). True

23. Which of the following effect has no contribution to deviate the ideal situation of a current mirror circuit?

- DIBL effects.

- Threshold offset between two transistors

- Channel length modulation

- Imperfect geometrical matching.

Ans: 1) DIBL effects.

24. What does the ASIC cell library contain?

- The physical layout of the cells

- Routing model of the cells

- Timing model of the cells

- All of the above.

Ans: 1) Physical layout of the cells.

25. Why does lowest propagation delay occur through a gate?

- Due to – strong transistor, high temperature, high voltage.

- Due to – strong transistor, low temperature, high voltage.

- Due to – Weak transistor, high temperature, high voltage.

- Due to – weak transistor, low temperature, low voltage.

Ans: 3) Due to – Weak transistor, high temperature, high voltage.

26. Which of the following is true about VLSI logic design?

- VLSI minimizes the area and delay

- VLSI minimizes the area at the cost of delay

- VLSI maximizes speed by decreasing area

- VLSI minimizes delay by reducing the area

Ans: 2) VLSI minimizes the area at the cost of delay.

27. What is a hard macro?

- Flexible Block

- Fixed Block

- Flexible block with a fixed aspect ratio

- Flexible block with a flexible aspect ratio

Ans: 2) Fixed Block

28. State True or False

Statement: The full form of SPICE is – Simulation Program with Integrated Circuit Emphasis.

- True

- False

Solution: (1). True

29. What is the equivalent circuit for CMOS comparator?

- Uncompensated CMOS OPAMP.

- Compensated CMOS OPAMP.

- Partially Compensated CMOS OPAMP.

- None of the above is true.

Ans: 1) Uncompensated CMOS OPAMP.

30. What is the relation between the equivalent resistance of a switched capacitor and the clock frequency?

- The resistance is proportional to clock frequency.

- The resistance is inversely proportional to clock frequency.

- The resistance is proportional to the square of the clock frequency.

- The resistance is inversely proportional to the square of the clock frequency.

Ans: 2) The resistance is inversely proportional to clock frequency.

30 Most important and frequently asked VLSI Interview Questions! Click Here!

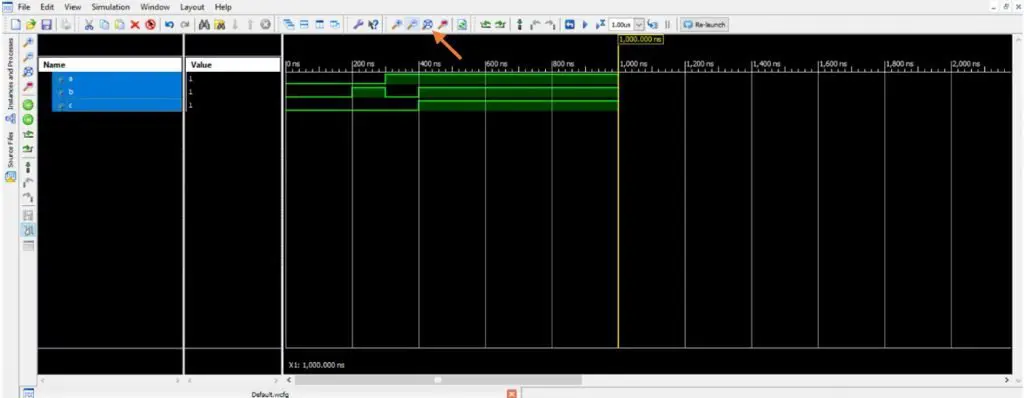

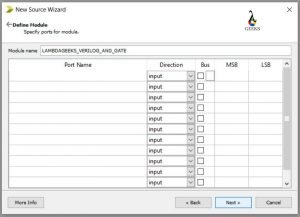

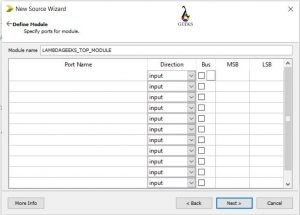

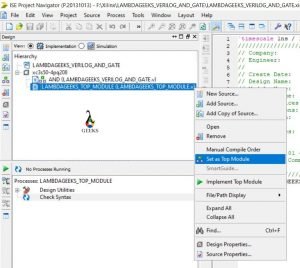

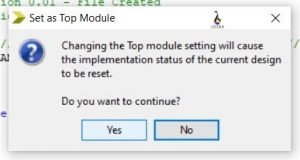

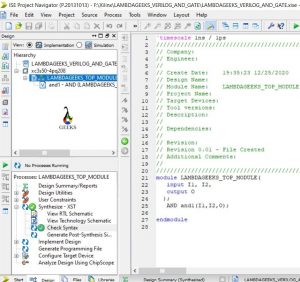

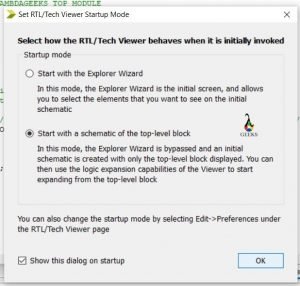

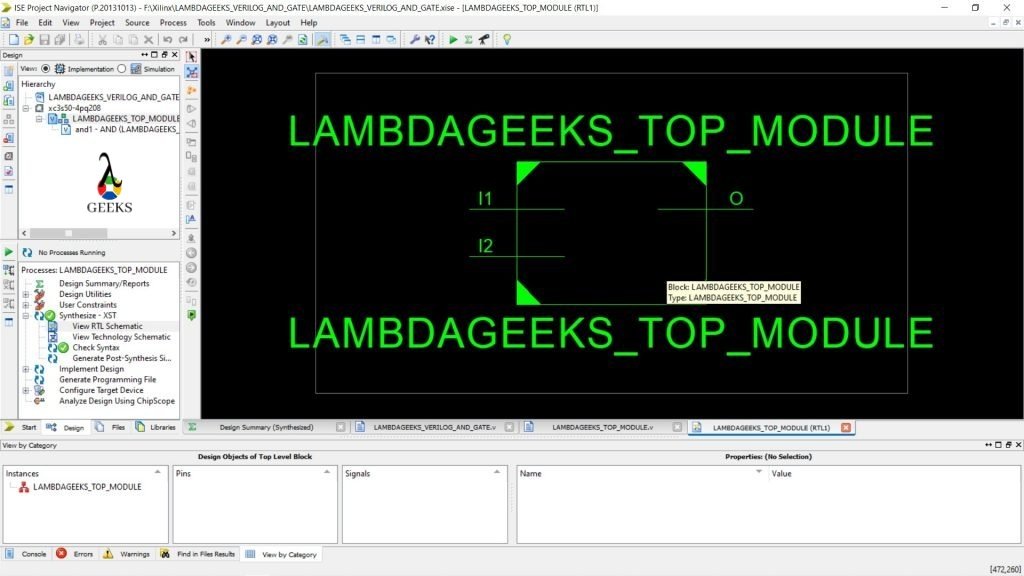

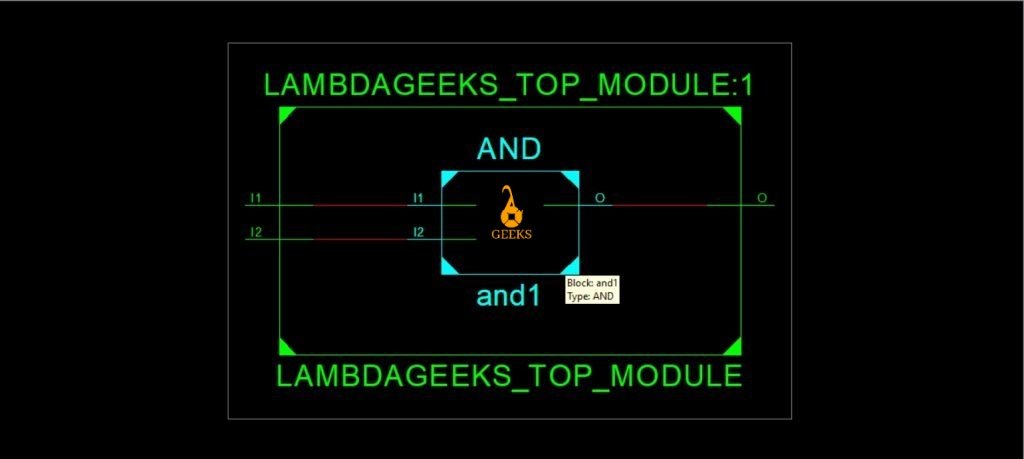

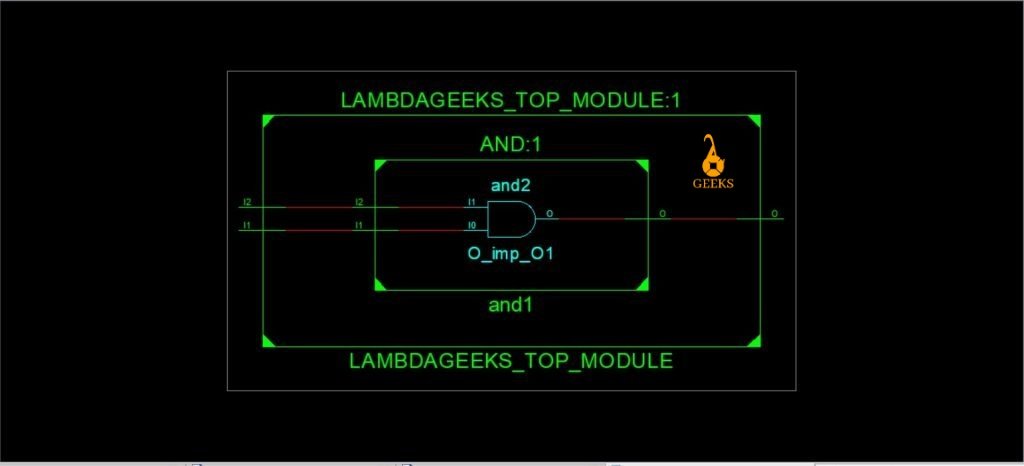

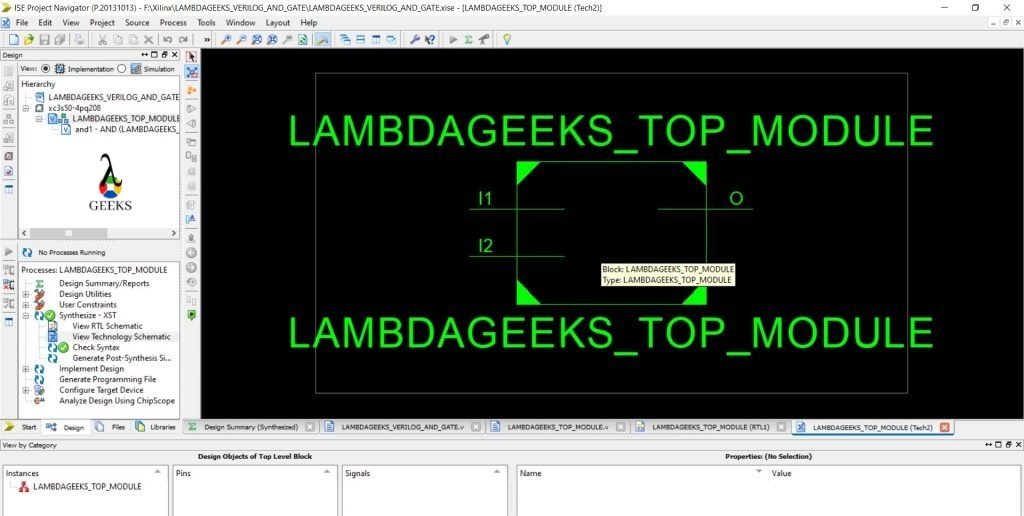

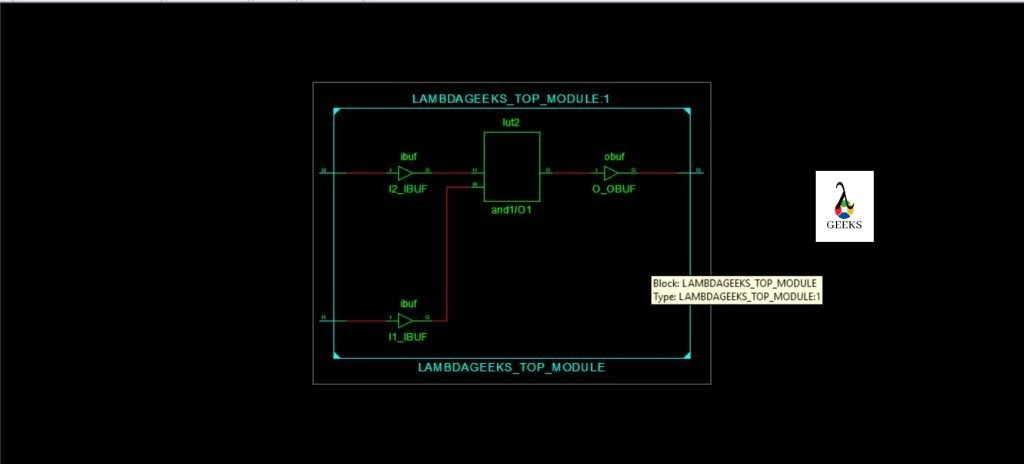

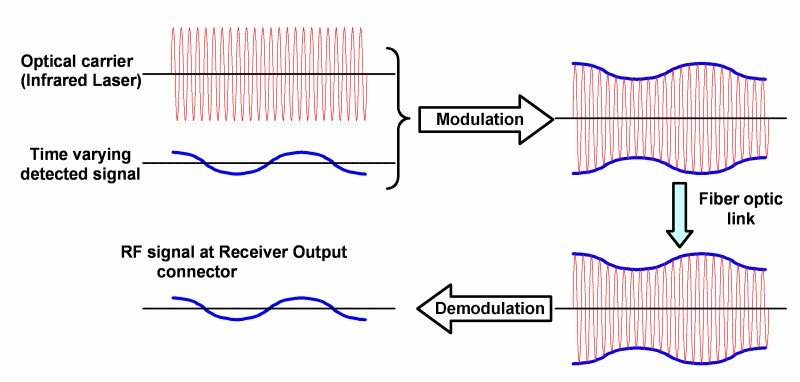

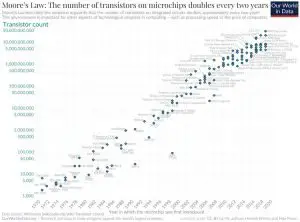

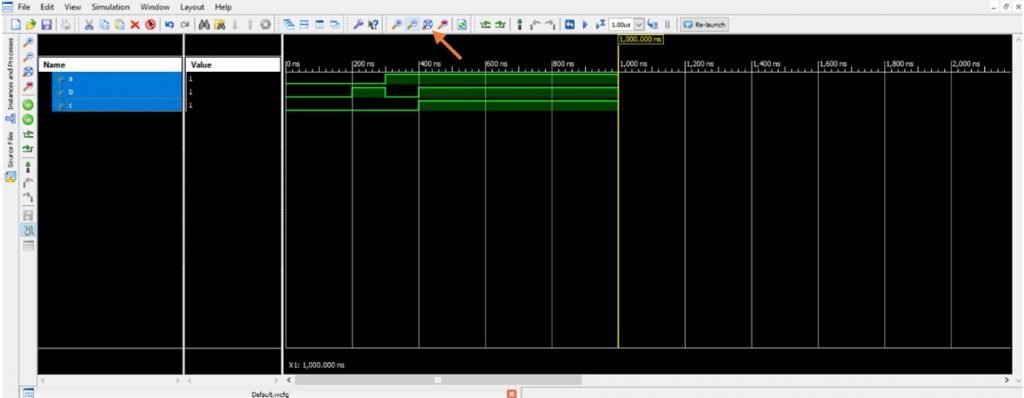

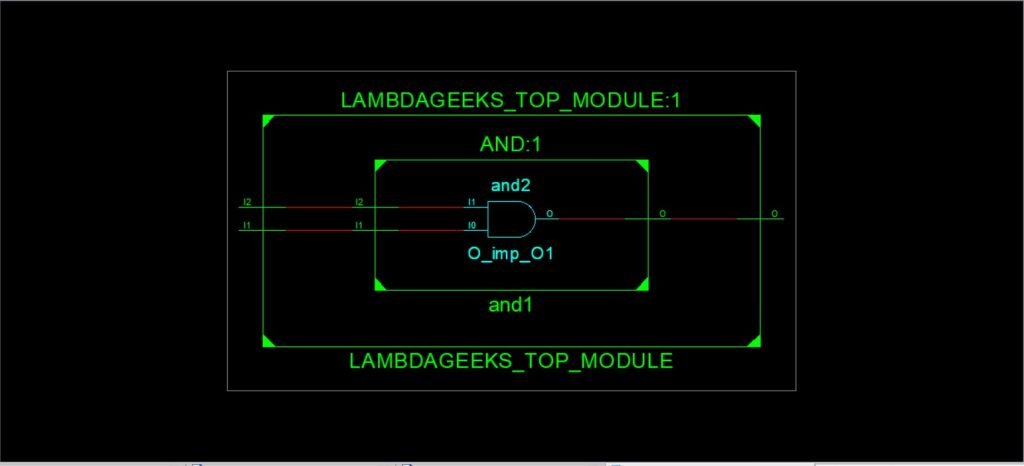

VLSI, VHDL, Verilog Interview Questions, Image – 3

31. What is the relation between the equivalent resistance of a switched capacitor and the capacitance?

- The resistance is proportional to the capacitance.

- The resistance is inversely proportional to the capacitance.

- The resistance is proportional to the square of the capacitance.

- The resistance is inversely proportional to the square of the capacitance.

Ans: 2) The resistance is inversely proportional to the capacitance.

32. What is the condition for domination by Diffusion Current?

- Strong Inversion

- Weak Inversion

- Both Strong and weak inversion.

- Cannot be determined.

Ans: 2) Weak Inversion.

33. What is the condition for domination by Drift Current?

- Strong Inversion

- Weak Inversion

- Both Strong and weak inversion.

- Cannot be determined.

Ans: 1) Strong Inversion.

34. State True or False

Statement: In the cascode current mirror, the output resistance is increased.

- True

- False

Solution: (1). True

35. State True or False

Statement: A current mirror circuit can be used as a current amplifier by increasing the (W/L) ratios of the mirrored and source MOSFET

- True

- False

Solution: (1). True

36. Which connections of NMOS in PDN, help to realize the AND terms?

- Cascade Connection

- Anti – parallel Connections

- Series Connections

- Parallel Connections

Ans: 3) Series Connections

37. Which type of transistor can pass logic-high value perfectly, but not the logic-low value?

- NMOSFET

- PMOSFET

- CMOS

- None of the above

Ans: 2) PMOSFET

38. What is the minimum number of transistors needed to design an XOR gate?

- Three

- Four

- Five

- Six

Ans: 4) Six

39. Which type of logic design provides the minimum propagation delay?

- Emitter Coupled Logic

- Transistor Transistor Logic

- Register Transistor Logic

- Diode Transistor Logic

Ans: 1) Emitter Coupled Logic

40. State True or False

Statement: Dynamic CMOS logic operates using two non-overlapping clock pulses.

- True

- False

Solution: (2). False.

For more VLSI related topic and Verilog interview questions click here