Points of Discussions

- Introduction to AC Circuit

- Important terminologies related to AC Circuit

- Pure Resistive AC Circuit

- Pure Capacitive AC Circuit

- Pure Inductive AC Circuit

Introduction to AC Circuit

AC stands for alternating current. If the flow of charge from an energy source changes periodically, the circuit will be referred to as an AC circuit. The voltage and current (both magnitude and direction) of an AC circuit changes with time.

AC circuit comes up with additional resistance towards current flow as impedance and reactance are also present in AC circuits. In this article, we will discuss three elementary yet important and fundamental AC circuits. We will find out the voltage and current equations, phasor diagrams, power formats for them. More complicated yet basic circuits can be derived from these circuit, like – Series RC Circuits, Series LC circuits, Series RLC circuits, etc.

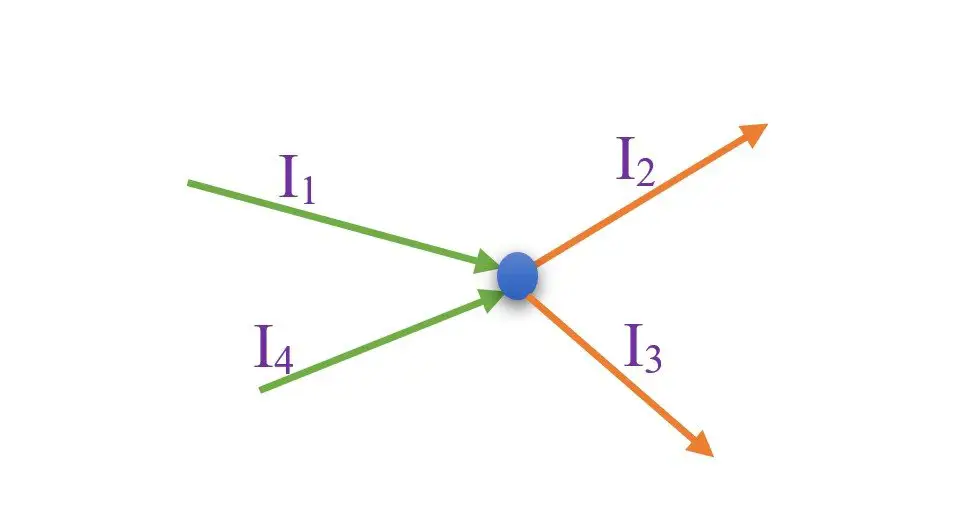

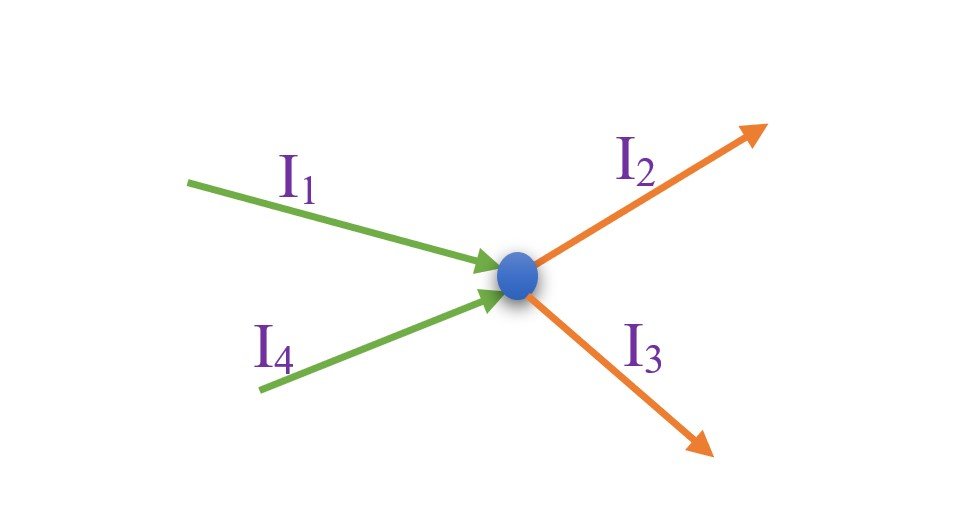

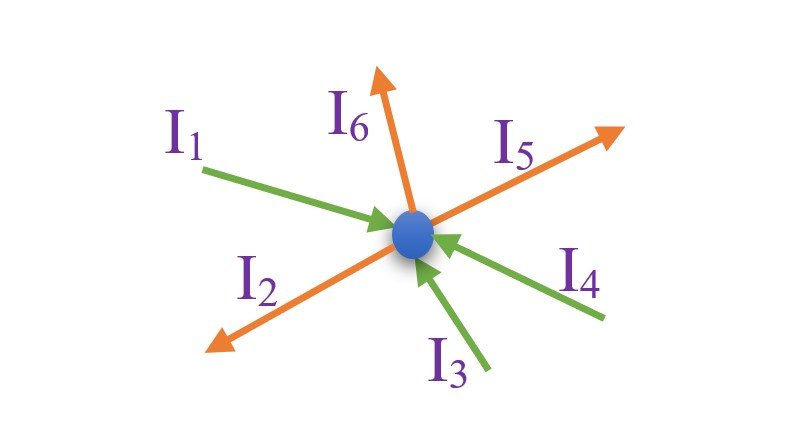

What is DC Circuit? Learn About KCL , KVL! Click Here!

Important terminologies related to AC Circuit

Analysing the AC circuit and studying them needs some basic knowledge of electrical engineering. Some of the frequently used terminologies are noted down below for references. Study them briefly before exploring the AC circuit family.

- Amplitude: Power flows in the AC circuit in the form of sinusoidal waves. Amplitude refers to the maximum magnitude of the wave that can be reached in both the positive and negative domains. The maximum magnitude is represented as Vm and Im (for voltage and current, respectively).

- Alternation: Sinusoidal signals have a period of 360o. That means the wave repeats itself after a 360o time span. Half of this cycle is referred to as alternation.

- Instantaneous value: Magnitude of voltage and current given at any instant of time is known as instantaneous value.

- Frequency: Frequency is given by the number of cycles created by a wave in once second time span. The unit of frequency is given by Hertz (Hz).

- Time period: Time period can be defined as the time span taken by a wave to complete one full cycle.

- Wave form: Wave form is the graphical representation of the propagation of waves.

- RMS values: RMS value means the ‘root mean square’ value. RMS value of any AC components represents the DC equivalent value of the quantity.

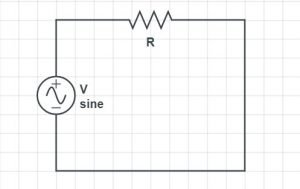

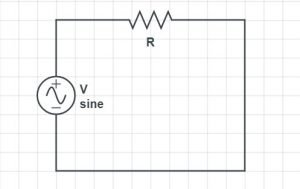

Pure Resistive AC Circuit

If an AC circuit only consists of a pure resistance, then that circuit will be called as Pure Resistive AC Circuit. There is no inductor or capacitor involved in this type of AC circuit. In this circuit, the power generated by the resistance and the energy components, voltage and currents, stay in an identical phase. That ensures the rise of voltage and current for the peak value or the maximum value occurs at the same time.

Let us assume the source voltage is V, the resistance value is R, the current flowing through the circuit is I. Resistance is connected in series. The below equation gives the voltage of the circuit.

V = Vm Sinωt

Now, from Ohm’s law, we know that V= IR, or I = V / R

So, the current I will be,

I = (Vm / R) Sinωt

Or, I = Im Sinωt; Im = Vm / R

The current and voltage will have the maximum value for ωt = 90o.

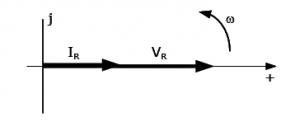

Phasor Diagram of a purely resistive circuit

Observing the equations, we can conclude that there is no phase difference between the circuit’s current and voltage. That means the phase angle difference between the two energy components will be zero. So, there is no lag or lead in between voltage and current of the pure resistive AC circuit.

Power in a purely resistive circuit

As mentioned earlier, current and voltage remain in the same phase in the circuit. The power is given as a multiplication of voltage and current. Proposed for AC circuits, the instantaneous values of voltage and current is taken into considerations intended for the calculation of power.

So, power can be written as – P = Vm Sinωt * Im Sinωt.

Or, P = (Vm * Im /2) * 2 Sinω2t

Or, P = (Vm /√2) * (Im/ √2) * (1 – Cos2ωt)

Or, P = (Vm /√2) * (Im/ √2) – (Vm /√2) * (Im/ √2) * Cos2ωt

Now for average power in ac circuit,

P = Average of [(Vm /√2) * (Im/ √2)] – Average of [ (Vm /√2) * (Im/ √2) * Cos2ωt]

Now, Cos2ωt comes as zero.

So, the power comes as – P = Vr.m.s *Ir.m.s.

Here, P stands for average power, Vr.m.s stands for root mean square voltage, and Ir.m.s stands for root mean square value of current.

Pure Capacitive AC Circuit

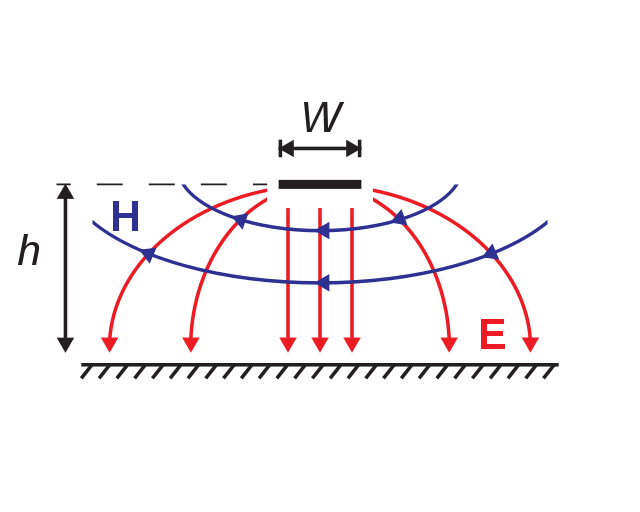

If an AC circuit only consists of a pure capacitor, then that circuit will be called as pure capacitive AC circuit. There is not any resistor or inductor involved in this form of AC circuit. A typical capacitor is a passive electrical device that stores electrical energy in an electric field. It is a two-terminal device. Capacitance is known as the effect of the capacitor. Capacitance has a unit – Farad(F).

When voltage is applied across the capacitor, the capacitor gets charged, and after some time, it starts discharging when the voltage source is taken away.

Let us assume that the source voltage is V; the capacitor has a capacitance of C, the current flowing through the circuit is I.

The below equation gives the voltage of the circuit.

V = Vm Sinωt

The capacitor’s charge is given by Q =CV, and I = dQ / dt gives the current inside the circuit.

So, I = C dV/dt; as I = dQ/dt.

Or, I = C d (Vm Sinωt)/dt

Or, I = Vm C d (Sinωt) / dt

Or, I = ω Vm C Cosωt.

Or, I = [Vm /(1/ωC)] sin (ωt + π/2)

Or, I = (Vm / Xc) * sin (ωt + π/2)

Xc is known as the reactance of the AC circuit (specifically the capacitive reactance). The maximum current will be observed when (ωt + π/2) = 90o.

So, the Im = Vm / Xc

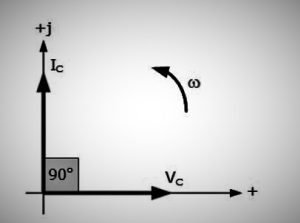

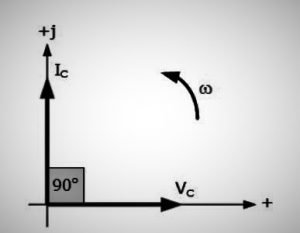

Phasor Diagram of Pure capacitive circuit

Observing the equations, we can conclude that the circuit’s voltage leads over the current value by an angle of 90 degrees. The phasor diagram of the circuit is given below.

Power in a purely capacitive circuit

As mentioned earlier, the voltage phase has a lead over current by 90 degrees in the circuit. The power is given as a multiplication of voltage and current. For AC circuits calculations, the instantaneous values of voltage and current are taken into consideration intended for the calculation of power.

So, power for this circuit can be written as – P = Vm Sinωt * Im Sin (ωt + π/2)

Or, P = (Vm * Im * Sinωt * Cosωt)

Or, P = (Vm /√2) * (Im/ √2) * Sin2ωt

Or, P = 0

So from the derivations, we can say that the average power of the capacitive circuit is zero.

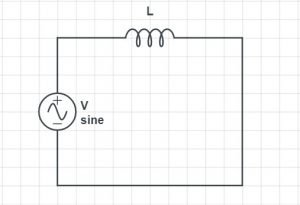

Pure Inductive AC Circuit

If an AC circuit only consists of a pure inductor, then that circuit will be called as pure inductive AC circuit. There is not at all resistors or capacitors are involved in this type of AC circuit. A typical inductor is a passive electrical device that stores electrical energy in the magnetic fields. It is a two-terminal device. Inductance is known as the effect of the inductor. Inductance has a unit – Henry(H). The stored energy might also be returned to the circuit as current.

Let us assume that the source voltage is V; the inductor has an inductance of L, the current flowing through the circuit is I.

The below equation gives the voltage of the circuit.

V = Vm Sinωt

The induced voltage is given by – E = – L dI/dt

So, V = – E

Or, V = – (- L dI/dt)

Or, Vm Sinωt = L dI/dt

Or, dI = (Vm/L) Sinωt dt

Now, applying integration on both sides, we can write.

Or, ∫ dI = ∫ (Vm/L) Sinωt dt

Or, I = (Vm/ ωL) * (- Cosωt)

Or, I = (Vm/ ωL) sin (ωt – π/2)

Or, I = (Vm/ XL) sin (ωt – π/2)

Here, XL = ωL and is known as inductive reactance of the circuit.

The maximum current will be observed when (ωt – π/2) = 90o.

So, the Im = Vm / XL

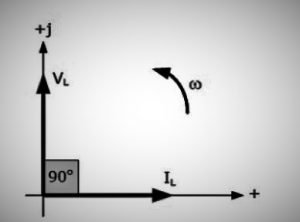

Phasor Diagram of Pure inductive circuit

Observing the equations, we can conclude that the circuit current leads over the voltage value by an angle of 90 degrees. The phasor diagram of the circuit is given below.

Power in a purely inductive circuit

As mentioned earlier, a current phase has a lead over voltage by 90 degrees in the circuit. The power is given as a multiplication of voltage and current. For Ac circuits, the instantaneous values of voltage and current is taken into considerations utilized for the calculation of power.

So, power for this circuit can be written as – P = Vm Sinωt * Im Sin (ωt – π/2)

Or, P = (Vm * Im * Sinωt * Cosωt)

Or, P = (Vm /√2) * (Im/ √2) * Sin2ωt

Or, P = 0

So, from the derivations, we can say that the inductive circuit’s average power is zero.