Voltage doesn’t always mean that it has to be positive. That’s why a question arises can voltage be negative or not? Let’s feed your curiosity about negative voltage.

This article explains how a voltage can be negative, explaining the sign convention of voltage (according to basic circuit sign convention) in various circuitry, what causes the negative voltage, and converting any voltage to negative voltage.

Is voltage positive or negative?

Voltage is the potential created between the two different points. Voltage can be elucidated as the work done per unit required to make a move for a unit charge from one point to another in presence of a static electric field.

Voltage has magnitude and polarity. The polarity of the voltage can be negative or positive, where is the magnitude of voltage can only be positive. Voltage is a relative quantity, so that it can be positive as well as negative.

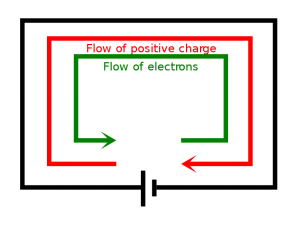

The concept of positive and negative voltage comes from the sign convention. The sign convention is a rule adopted globally to define electric flow or signs of electric power in a circuit. Benjamin Franklin was the one who surmised that electric flow from the positive terminal of voltage to the negative voltage terminal. At that time, the role of the electron in current flow was not clear the convention given by him to get accepted. Still, later on, after several discoveries, it was found that electron which causes current travel in the opposite direction of the current flow.

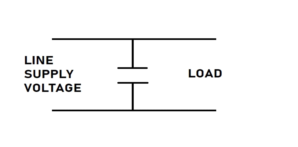

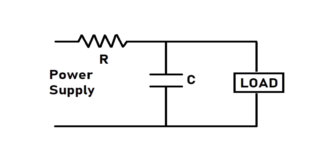

In-circuit zero volts are referred to as the ground, which is taken as a reference to measure other voltages. The voltage polarity of an electric circuit element varies for active or passive element for a passive element such as resistor The Terminal through which electron enters the element that terminal is the negative voltage terminal and another terminal of the component is the positive voltage terminal. For active components such as power supply and capacitor, the terminal that delivers current is the positive terminal, and the other terminal is the negative terminal.

What does it mean when voltage is negative?

Voltage is a relative quantity, so that it can be a negative or positive value.

When the voltage is more negative (in polarity) with respect to the circuit’s ground, then the voltage is negative.

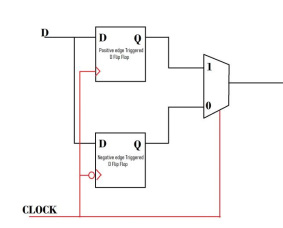

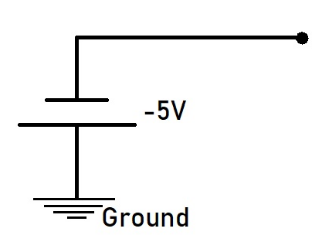

For example, a DC voltage source such as a battery (or cell) has a negative and positive terminal. When the battery’s positive terminal is founded, the negative terminal is connected to the circuitry then the voltage provided through the supply to the circuit is a negative voltage.

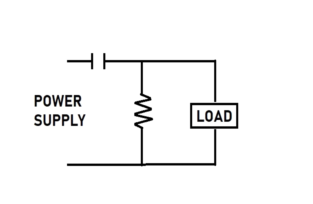

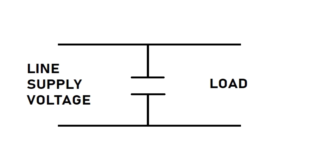

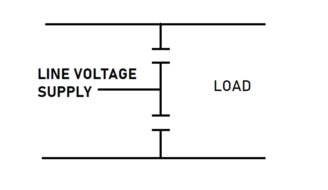

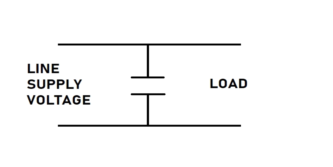

The positive or negative voltage can be due to the orientation of voltage supplies in the circuitry. When the negative terminal is directly linked to the ground and the positive terminal is directly linked to the circuitry, the voltage generated is the positive voltage. When the positive (+) terminal linked directly to the ground, and the negative (-) terminal is linked to the circuitry, the voltage generated out of the negative(-) terminal of supply is the negative voltage.

What is Negative Voltage used for

Several circuits use negative voltage, such as a transistor, Telecom, push-pull amplifier, a power driver circuit, etc.

Use of negative voltage:

The operational amplifier (OpAmp) needs both positive and negative voltage for proper operation and amplification. For transistor biasing, a negative voltage is one requisite. In telecommunication, the lines are buried underground in the presence of moisture and other external material, which can cause corrosion in the wire, which is generally made of copper. When a negative voltage is used through the wire, it minimizes the corrosion.

Can Voltage Gain be Negative ?

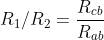

Voltage gain is the ratio of output voltage (in volt) to the input voltage (in volt) of an circuit element.

Negative voltage gain means there is a change in polarity of the voltage from input to output. In other words, the output voltage is 180 degrees out of phase concerning the input. Voltage gain is negative when the output voltage is less (due to attenuation or phase shift) than that of the input voltage. A negative feedback amplifier has a negative voltage gain.

Can a battery voltage be negative?

Battery voltage polarity depends upon how it is connected between the circuitry and the ground.

Suppose the battery’s positive (+) terminal is directly linked to the ground and the negative (-) terminal is linked to the circuit. In that case, the voltage generated from it will be negative, and if the negative terminal is grounded.

The positive terminal is connected to the circuitry, then the voltage generated from it will be positive.

What is Negative Voltage in AC ?

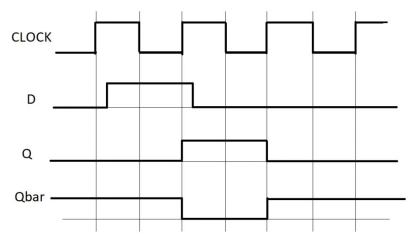

In an alternating current (AC) circuit, two poles of the AC source interchanges between positive and negative.

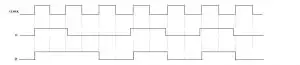

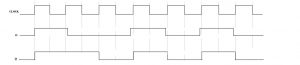

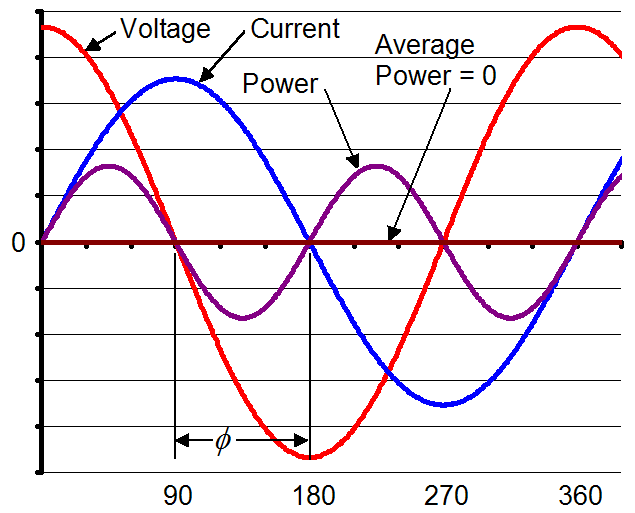

The negative voltage in AC means the voltage is 180 degrees out of phase concerning the positive voltage. A complete cycle of AC consists of two half-cycle one is positive (+) half, and the other is the negative (-) half. The positive half is where the voltage is positive at any instant. Still, during the negative half of the circle, the polarity of voltage gets inverted with respect to the positive half of the cycle, which means at any instant of time during the negative half cycle, the voltage is negative.

Can Thevenin Voltage be Negative?

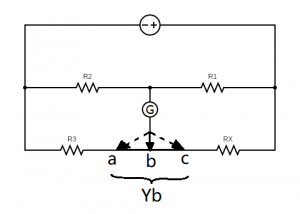

Thevenin voltage can be defined according to the Thevenin theorem, which states that any linear circuitry is a combination of several voltage sources, and resistors can be replaced by a resistor and a voltage source; the resulting voltage source is the Thevenin voltage.

The polarity of Thevenin voltage can be negative and positive depending upon the orientation of the Thevenin voltage in the circuitry. If the calculated Thevenin voltage is negative, that means the direction of the resultant power source will change. If the calculated value remains positive, then the orientation of the resulting power supply orientation is correct.

Can RMS Voltage be Negative ?

RMS stands for route mean square value. RMS voltage can be obtained by taking the square root of the mean value of squared instantaneous voltage over a time interval

The outcome of a square root can be negative or positive. Suppose the amplitude of the voltage is taken for the RMS, then by convention. In this case, the RMS of the voltage will only be positive if amplitude and phase of the voltage are taken for obtaining RMS voltage, then it can be a complex negative or positive value.

Can Node Voltage be Negative ?

In a circuit, the node is a point between two or more circuit elements, and node voltage is the electric potential difference between two nodes of the circuit.

Node voltage can be positive or negative as it is a relative quantity. One node of the circuit can be considered as a reference node, and with respect to that node, another node voltage can be measured. Generally, the reference voltage is the ground node, so the other node’s value depends on the direction of the current orientation, etc., with respect to the reference node. The measuring node voltage may be inferior than that of the reference voltage.

Can Stopping Voltage be Negative ?

In the Photoelectric effect experiment, the anode is the target material. The anode is connected to the positive terminal of the voltage source while exposed to the monochromatic and electromagnetic wave, which results in current flow through the circuit current is called photocurrent.

When the anode is linked to the negative terminal of the voltage source, as the voltage increases, the photocurrent dies out. The voltage at which the photocurrent stops flowing through the circuit is known as the stopping voltage. Through this experiment, we got to know that the stopping voltage is a negative value.

Can Peak to Peak Voltage be Negative ?

Peak to peak voltage is the difference between minimum voltage and a maximum voltage of a voltage signal.

The magnitude of the peak to peak voltage can vary from 0 to any positive value as the polarity of peak to peak voltage can be negative and positive.

Can Instantaneous Voltage be Negative ?

Instantaneous voltage is the value of the voltage ( or potential difference) at a particular moment of time.

Instantaneous voltage can be negative or positive. The instantaneous voltage of a negative DC voltage source is consistently negative at any instant of time. In AC voltage, the instantaneous voltage varies from positive to negative with time. For the negative cycle of the AC voltage signal, the instantaneous value of the voltage is negative at any instant in time.

Is Current Negative if Voltage is Negative?

Voltage is a relative quantity so that it can be negative. Negative current can only mean the direction of electron current, which is opposite to the electrical current as of the convention.

Negative voltage means the supply’s negative terminal is directly connected to the circuitry, and the positive terminal is grounded. The current from the negative(-) terminal of the voltage source is taken into consideration . That current will be the negative current as we know the electrical current from the positive terminal of any voltage supply.

What does Negative 5 Volts mean?

5 volt is a potential difference (or voltage) between two different points. Acknowledge that voltage is a relative quantity, the polarity of the voltage can change considering the references.

When the positive terminal of the 5 DC volt supply is directly linked to the ground. As a result, the positive (+) terminal becomes the reference voltage, and the negative (-) terminal of the 5 volt supply is linked to the circuitry. The resultant voltage through the 5 volt supply will be negative 5 volts as the positive terminal is taken as the reference point.

How do you create a Negative Voltage?

Different methods can be used to generate a negative voltage.

Using :-

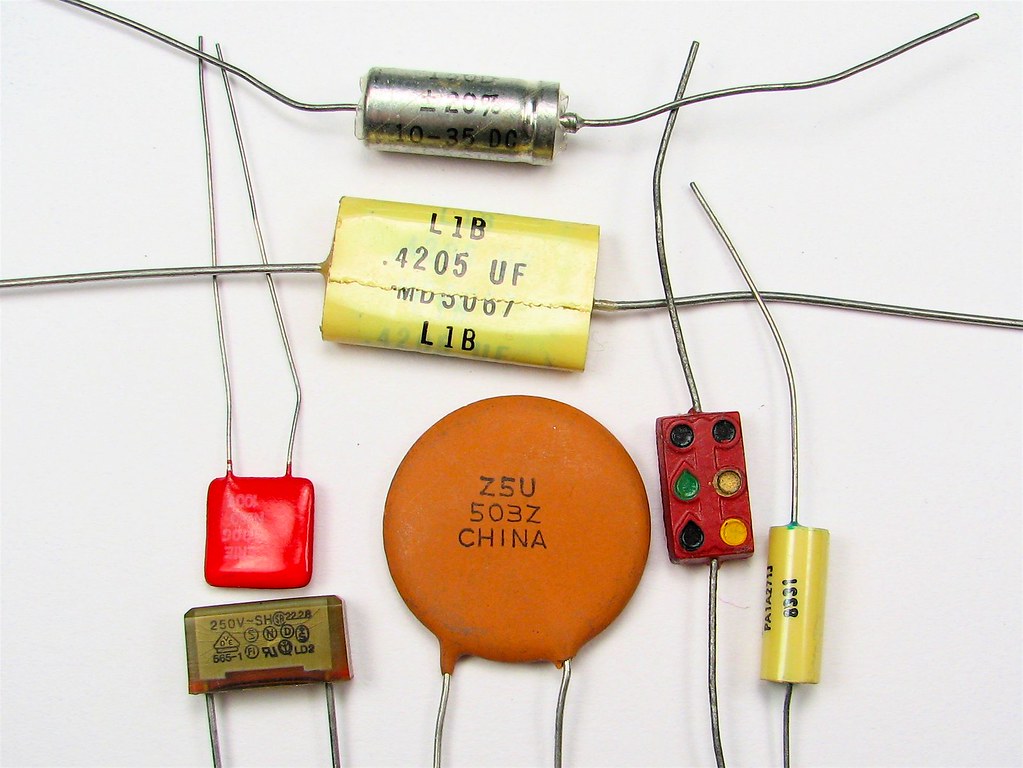

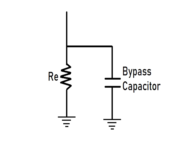

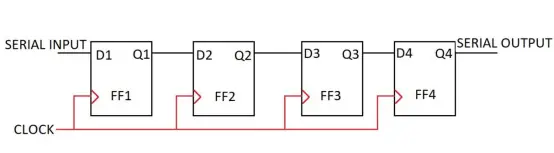

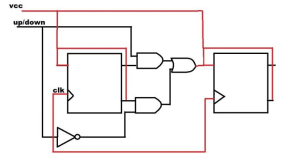

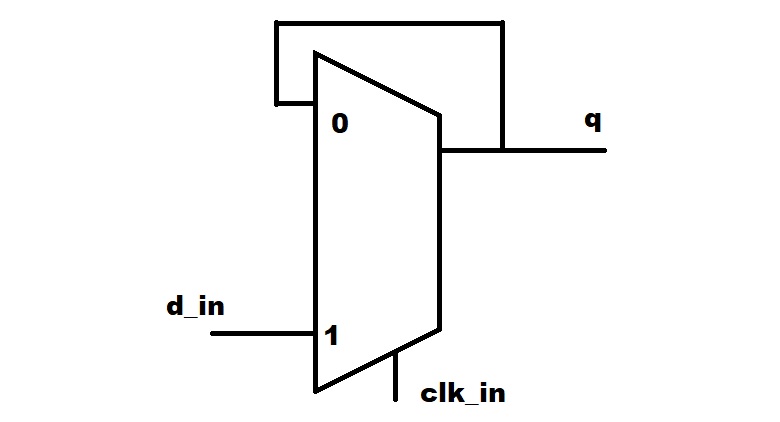

With the combination of 555 timers and a clipper circuit, the negative voltage can be generated as output. Here 555 timer act as an astable vibrator. After receiving power from the power supply, 555 will generate a square wave as an output, which will consist of both positive and negative voltage. During the positive half of the output voltage, the capacitor connected with the output gets charged, so there will be no positive voltage. During the negative voltage at the capacitor gets discharged through the diode providing negative voltage as output.

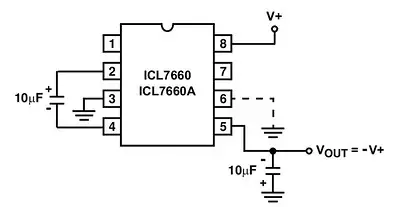

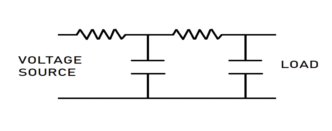

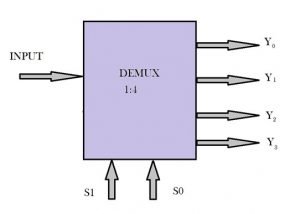

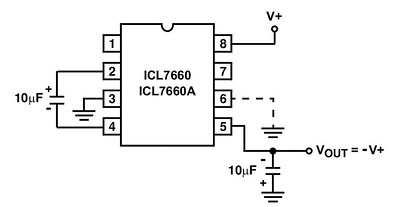

There are several ICS that uses switched capacitor voltage converter to convert a voltage into a negative voltage. Generally, these IC contains non-critical capacitors for the charge pump and charge reservoir. And as the fundamental component of these ICs is oscillator voltage level translator and MOS switches.

As we know half-wave rectifier can filter out positive or negative half of any AC signal as required output is the negative voltage negative half-wave rectifier can be used in this rectifier only negative half of the AC signal can pass through it so as a result, there will only be the negative voltage as output

The voltage gain of inverting amplifier is negative, which means the output of the inverting amplifier is 180 degrees out of phase with the input of the amplifier, so if a positive voltage is fed into the inverting, amplifier, then the negative voltage will be as output.

How do you convert Negative Voltage to Positive?

Negative voltage can be converted into positive voltage as a requirement.

Inverting amplifier can be used to transform the negative (-) voltage into positive(+) voltage. The voltage gain of the inverting amplifier is negative, which means the output voltage is 180 degrees out of phase concerning the input. If the input is taken as a negative voltage, then the output voltage of the inverting amplifier will be positive.

What are Negative Voltage Regulators?

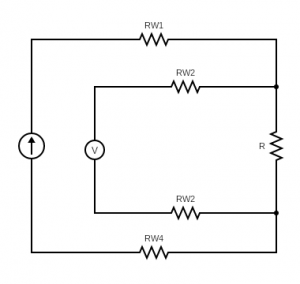

Voltage regulators are used to maintaining a specific range of voltage for different purposes.

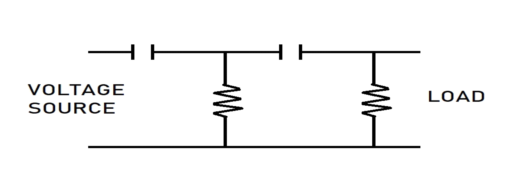

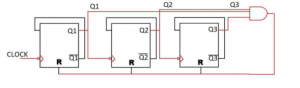

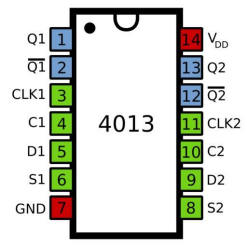

A negative voltage regulator is a circuit that is used to maintain the voltage of any specific negative voltage range. 79XX is an IC family which is a three-pin negative voltage regulator.

These ICs are available in 3 different output voltages -5, -12, and – 15. These integrated circuits have intercurrent limiting properties and thermal shutdown protection for their safety.

Can Arduino Output Negative Voltage?

There are several Arduino boards available commercially.

Generally, the output voltage directly from Arduino is in the positive voltage range. The voltage range will vary from one type to another or the pin from which output is taken. For getting negative voltage output from Arduino, external voltage converter circuitry is required for the voltage conversion from positive to negative.

Is Ground Positive or Negative?

The ground is the reference point of the circuitry with respect to which the voltage of any point can be measured.

The ground can be positive as well as negative depending upon the design of the circuitry. In electronics, a positive or a negative terminal of any power supply can be considered the ground. When the supply’s negative terminal is directly connected to the ground, then the ground is called negative ground. When the supply’s positive terminal is directly connected to the ground, then the ground is called positive ground.

Can you Connect Ground to Negative?

The voltage source has two terminals; one is considered positive, and the other is negative.

The ground is the Zero Volt reference point of the circuit. If there is only one supply in the circuit, then the supply’s negative terminal is considered the same as the ground. If required, the ground can also be linked directly to the negative (-) terminal of the DC supply. When the DC terminal is directly connected to the ground, then the ground is called negative ground. There is no positive or negative end in AC supply as polarity changes with time, so a neutral wire from the AC circuit can be directly connected to the ground. The ground is not necessary for every circuit. It is generally used for protection, a common reference point for voltages, etc.

How do you test a Negative Voltage Regulator?

The output and input voltage of the regulator can check for testing the negative voltage regulator.

The input voltage to the negative regulator can be measured with respect to the ground; the regulator’s input voltage is tested so that the regulator can work appropriately with sufficient input voltage. The input voltage must be greater than that of the regulated output voltage in magnitude. The output voltage range differ with distinct voltage regulators. As for the negative voltage regulator, the output voltage range will be in negative voltage values. When a negative voltage regulator is tested, ensure the output voltage is in the negative voltage range. The voltage output must be nearby its rated output voltage. If the output voltage is not around the rated output, then the regulator may be defective.

Which IC is used to get Negative Voltage?

Switched capacitor voltage converter that inverts, divides, doubles, or multiples, the positive input voltage.

IC’s used to get the negative voltage as output are TL7660, MAX1044, NCP1729, LT1026, MAX870, MAX829, LT1054, CAT7660, etc. These IC’s are used in line drivers, operational amplifiers, suppliers, negative voltage generators, voltage splitters, voltage developers, etc. These ICs work for a different range of voltage that’s depends on the specifications of the IC.

Why does Current Flow from Negative to Positive?

The potential difference between the two points in the circuit is the flow of current.

The electron current begins from the negative (-) terminal. It travels to the supply’s positive terminal, as the electron current is in the contradictory direction of the electric convention of current. The flow of electrons is caused by the difference in polarity or the potential difference created by the excess of the electron at one end and the deficiency of electron at other—negatively charged electrons drawn towards the positive end of the supply from the negative end the supply.

What is difference between Positive and Negative Voltage?

Any voltage can be either positive, negative, or zero.

The difference between positive (+) and negative (-) voltage is in the polarity of the voltage. The polarity of the voltage can change with the reference as if a higher potential point is taken as a reference to measure the lower potential. The potential difference will be negative, which is the negative voltage. And when a lower potential point is taken as a reference to measure the higher potential, the potential difference will be positive. The polarity of voltage also influenced the orientation of the DC source. For AC source with time, the polarity of the voltage changes as for the positive half of the AC signal, the voltage is positive, and for the negative half, the voltage is negative.