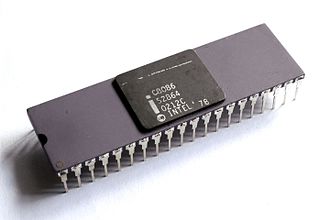

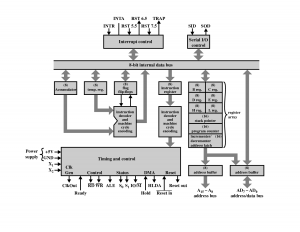

Define Registers of Microprocessor 8085:

“A register is a temporary or short term storage space built into a CPU.”

More or less of the registers are applied internally but they cannot be accessed outside the processor.

What are the Types of the Register in Microprocessor 8085?

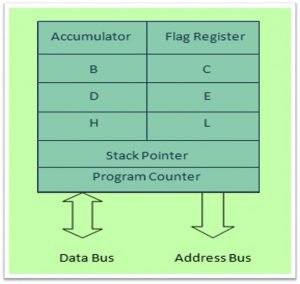

- Accumulator (8 bit)

- GPR (8 bit)

- SP (16 bit)

- PC (16 bit)

- IR (8 bit)

- TR (8 bit)

Define Accumulator:

In the microprocessor 8085, accumulator specified as an 8 bit register connected with an ALU. This is utilized to hold one of the operand for arithmetical and logic-operation; it works as input to the ALU. The other operand for arithmetic and logical operation possibly stored either in memory or in GPR. But the final product will be stored in the accumulator only.

Define General Purpose Register (GPR):

8085 microprocessor has 8 bit GPR; it works like a pair – B-C, D-E, H-L

The H-L register pair is used as a memory pointer & it holds 16 bit address of a memory location.

Define Stack Pointer (SP):

Stack pointer is a 16 bit especial purpose register. Stack is a order of memory location set by a programmer. The stack also perform as LIFO (Last in First Out). Here two operations are used; PUSH & POP.

Program Counter Definition:

A 16 bit register for specified operations ; comprises registers to load memory address from wherever the subsequent instruction is to be fetched.

Assume the program counter contains a memory location 7100H, this imply that microprocessor 8085 intended to fetch the instruction at the location 7100H.

Subsequently fetching the 7100H, the program counter is inevitably increses one count. This has the track of memory address of the instruction.

EXAMPLE: JMP, CALL, RETURN, RESTART etc.

Define Instruction Register:

This is an 8 bit register to hold the OPCODE of the instructions that has to be decode and execute. This is not accessible to the program writer.

Define Temporary Register:

This is a 8 bit non-programmable register utilized to keep data through an arithmetic and logical instruction implementation. TR is keeping intermediate results only and ultimate finalized end result is saved in the accumulator. This is microprocessor dependendent, not controlled by developer code.

Addressing Modes of Microprocessor 8085:

What is Addressing Mode?

“Addressing mode is the best way to define a certain data to be controlled by means of an instruction.”

Microprocessor has various kinds of addressing mode as it gives flexibility to the developer to get info and acessing data.

What are the types of Addressing Mode?

There are total five category as follows:

- The Direct Mode

- The Register Mode

- The Immediate Mode

- The Register Indirect Mode

- The Implicit Indirect Mode

Direct Addressing Mode (DAM):

In this mode the address of the operand is identified the instruction the aforementioned. Instruction that includes direct address require 3-bytes of storage space of Microprocessor 8085.

- Instruction Code

- 16 Bit Address

Sample instruction like STA 2500H stores the content of the accumulator in the memory location noted 2500H. Here 2500H is the address located in memory space where data is has be kept in.

Register Addressing Mode:

Here the operands are GPR. The opcode identifies the address of the register in addition to the operation to be executed.

For example the instruction MOV A, B will move the data of register B to register A. In other instruction like ADD B, A; will first doaddition operation with the data of register B to register A and the end result is to be stored in register A.

Immediate Addressing Mode:

Here the operands are specified within the instruction itself, that means when any data has to be performed then immediately the operation is executed.

Example – MVI 05

ADI 05

Register indirect Addressing Mode:

In this case the operand will be identified by the register-pairs. Here accumulation is not linked directly.

Example are H-L, B-C, D-E etc.

Implicit Addressing Mode:

There are certain instructions which operates on the content of operator. These instructions will not call for address of operand.

Example – JMP, CALL, RAR

Timing Effects of Addressing Modes:

Addressing modes influence both the quantity of time necessary for executing an instruction and the total amount of memory necessary for storing. By way of instance, instructions which use suggested or register fixing, execute quickly because they deal directly with the chip hardware or with information present in hardware registers.

Most significant, however instruction can be fetched using one memory access. The Amount of memory accesses necessary is the factor in determining performance time, more memory accesses thus require more implementation time.

For example, to executing a CALL instruction requires 5 memory entrees; out of these 3 will be for the access the entire instruction and the 2 will be for PUSHing the contents of the program counter onto the stack location.

The processor can access memory during every processing cycle. Each cycle includes a varying number of states. This is dependent upon the clk freq, and which might vary from 480 nSec to 2µsec. The 8085 have clk freq around 5 MHz and so a minimal state may be of 200 nanosec.

What is Subroutine?

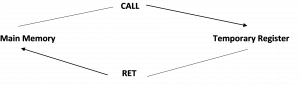

Creating a program of specific operation may happen several occasions and they’re not accessible as individual directions along with the application for such operation replicated over and over. However, the program ought to be written. The idea of subroutine is used to prevent the repetition of this smaller coding. The little program for specified for small job is called subroutine.

Subroutines are composed individually then saved to the primary memory by utilizing RET. CALL instruction is generally utilized from the primary memory to subroutine.

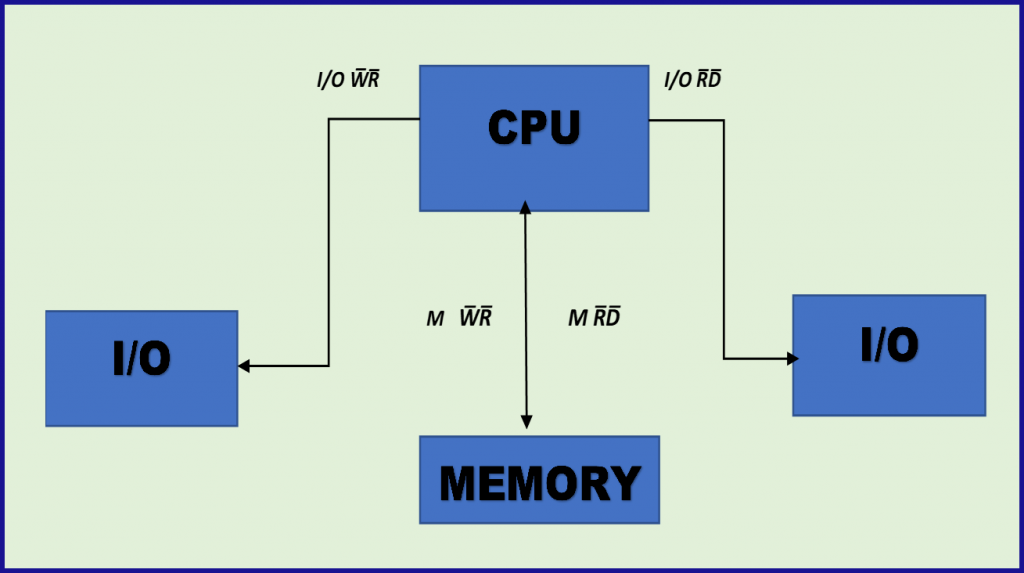

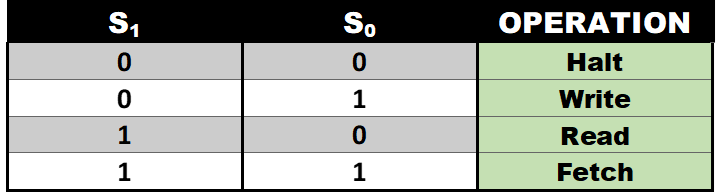

Instruction Cycle of Microprocessor 8085:

This is the time taken by the microprocessor to finish the execution of the instruction. An instruction cycle usually consists of 1 to 6 machine cycles.

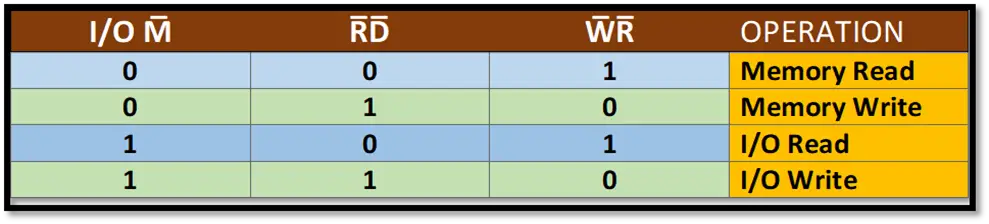

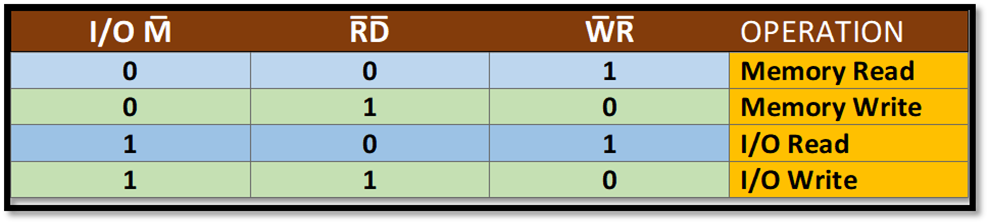

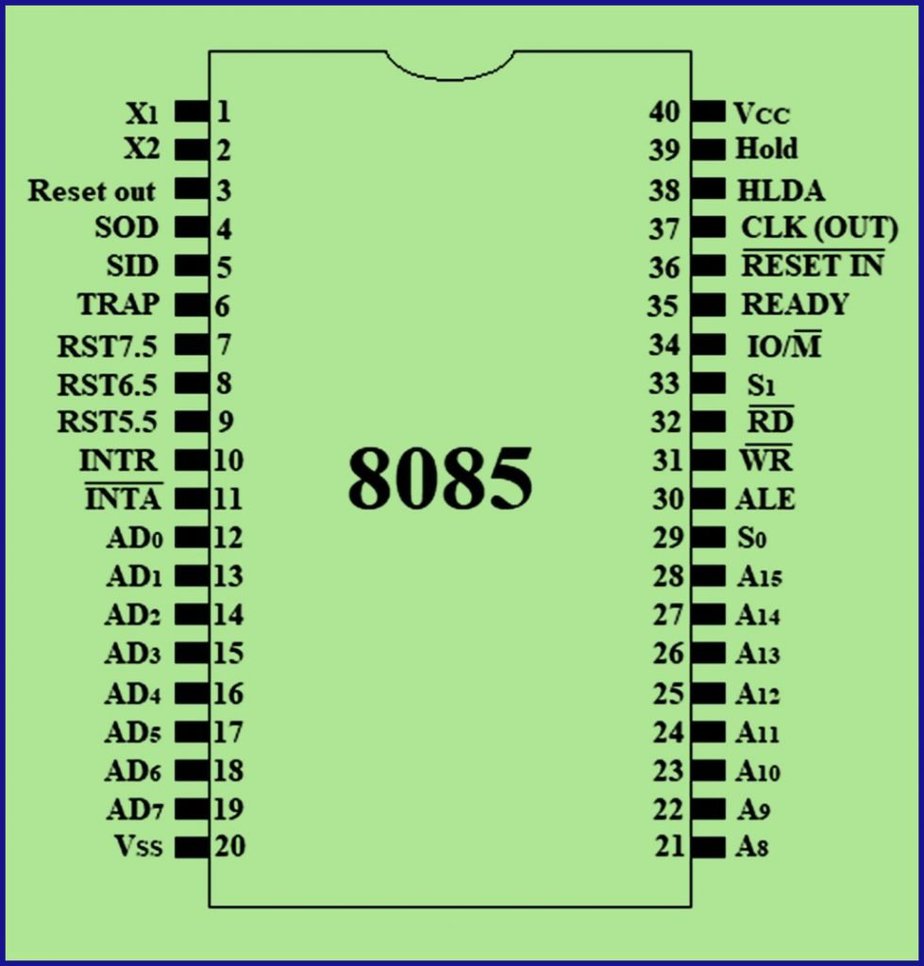

Machine Cycle

It is the time prerequisite to finish an operation through access one or the other the memory or I/O devices. It consists 3-6 T states. Here, opcode fetch, memory read, memory write, I/O read-write, operation executed. In the other word the operation of retrieving either memory devices or I/O devices is termed machine cycle.

T State:

This is the time equivalent to the one clock period in the basic unit used to calculate the time taken for the execution of the instruction and program in the microprocessor.

Fetch Operation:

The very initial byte of an instructionset is the OPCODE. An instruction usually more than 1 byte length. Another byte is for information data or for the operand address. At the start of the cycle that the info of program counter where opcode can be obtained is forwarded to the memory. This required 3 clock cycle another one is undefined.

What is the difference between CALL & JMP instructions of of Microprocessor 8085?

After a jump instruction is performed, the address given in JMP instruction is moved to PC. Thus application control is automatically progressed to this place location and carrying out as continued execution.

When CALL instruction is completed, microprocessor first keep PC info in the stack. Subsequently PC is occupied with the address set in the CALL instruction.Hence program control will transfer there.

What is Conditional & unconditional JUMP?

The JUMP commands are two kinds, specifically ‘unconditional jump’ and ‘conditional jump’. If the microprocessor is indeed initiated to load a new address in the PC and commence instructions in that, it’s termed as an unconditional jump. In the instance of a conditional jump, the PC is loaded with a new address only when certain conditions are created from the microprocessor after reading the correct status of register bits.

For more Electronics related article click here