Content :

Verilog was originally for stimulation and verification of digital circuits, it is a hardware description language (HDL). Here, all the code is designed with D flip flop whether VHDL or Verilog code.

Verilog Code for D flip flop using NAND gates

module nand_g(c, a, b); //*each module contains statements that defines the circuit, this module defies a NAND gate which is named as nand_g*//

input a, b; / a and b is the input variable to the NAND gate

output c; / output variable of NAND gate is defined

assign c = ~(a & b); / this assign is used to derive the value of c through a and b

endmodule /module end with endmodule statement

module not_g(e, f); / this block defines the NOT gate

input f; / f is the input variable to the NOT gate

output e; / e is the output variable of the NOT gate

assign e = ~f;

endmodule

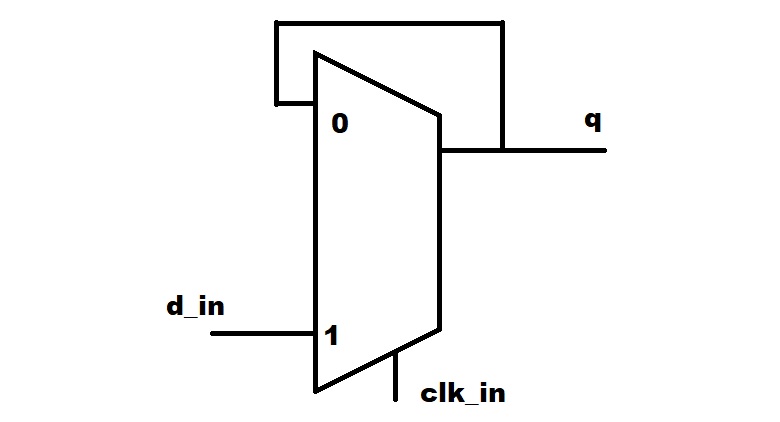

module d_ff_st(q_out, qbar_out, d_in, clk_in );

//* this module defines a d flip flop which will be design with NAND gate and NOT gate *//

input d_in, clk_in; / input variable of D flip flop d_in is the data input and clk_in is the clock input

output q_out, qbar_out; / output of the D flip flop q_out and qbar_out where q_out and qbar_out is compliment to each other

not_g not_1(dbar, d_in); /NOT gate module is called with dbar and d_in parameter

nand_g nand_1(x, clk_in, d_in); /NAND gate module is called with x, clk_in and d_in parameter

nand_g nand_2(y, clk_in, dbar); /NAND gate module is called with y, clk_in and dbar parameter

nand_g nand_3(q_out, qbar_out, y); / NAND gate module is called

nand_g nand_4(qbar_out, q_out, x); / NAND agte module is called

endmoduleVerilog Code for D flip flop with Asynchronous Reset

module dflip_flop_asy_rst (q, d_in, clk_in, reset_in);

input d_in, clk_in, reset_in; / input variables of the d flip flop is defined

output reg q; / output variable of the d flip flop is defined

always@ (posedge clk_in or posedge reset_in)

//* always block is the block who's statements are executed sequentially here the block will executed when clk_in is in positive edge or reset_in is in positive edge *//

if (reset_in) / if reset_in is high or true then q <= 1'b0

q <= 1’b0; / here 1'b0 means one bit number value zero

else / if reset_in is low or false then q<= d_in

q<=d_in;

endmodule / end of the module

Verilog Code for D flip flop using Dataflow Modelling

//*

Dataflow modeling provides the descriptions of combinational circuits by their function rather

than by their gate structure.*//

module dflipflo (q, d_in, clk_in); / module defines d flip flop in data flow modelling

input clk_in, d_in ; / input variable of the d flip flop

output q; / output variable of the d flip flop

assign q = clk_in ? d_in : q; / if clk_in is true the q = d_in and if clk_in is flase the q = q

endmodule

D flip flop Behavioral Verilog Code

//* Behavional is used when cicruit is sequential circuit it contain procedural statements *//

module dflip_flop_bh (q, d_in, clk_in);

input d_in, clk_in; / input variable of d flip flop is defined

output reg q; / output variable of the d flip flop is defined

always @ (posedge clk_in) / the block is takes place continuously when clk_in is in its positive edge of the pulse

if(clk_in) / if clk_in is high or true then q<=d_in

q<=d_in;

endmoduleVerilog Code for Shift Register using D flip flop

//* this code is used to designed 4 bit shift register using d flip flop, here left to right shifting is taking place through this code*//

module shift_reg_LtoR (out, clock, reset_in, in);/ this module define left to right shift register of 4 bit

input in, clock, reset_in; / input variable is defined

output out;

output reg [3:0] s; / output varible s is defined as a register that can have 4 bit value

always@ (posedge clock, negedge reset_in)

//* the sensitivity of this block is negative edge of reset_in or positive edge of clock *//

\t

if(!reset_in) / if else statement

s<=4’d0;

else

s<={ s [ 2 :0], in}; //* as s can have 4 bit value the s[2 : 0] has 3 bit and in has 1 bit, together they produce the 4 bit of s *//

assign out= s[3];

endmodule4 bit Ripple Counter using D flip flop Verilog Code

//* following code is for 4 bit ripple counter designed with d flip flop*//

module dff_r (input d_in, clk_in, rst_in, output reg q, output q_n);

//* module define a d flip flop with clock, reset, d, as input, and q and qbar as output *//

always@(posedge clk_in or negedge rst_in) //* this block sensitivity is positive edge of clk_in pulse or negative edge of rst_in *//

if (! rst_in) / if rst_in is low or false the q is implemented with zero

q<=0;

else

q<= d_in;

assign

q_n <= ~q;

endmodule

module ripple_c (input clk_in, rst_in, output [3:0] o); / this module define the ripple counter of 4 bit

wire q_0, qn_0, q_1, qn_1, q_2, qn_2, q_3, qn_3; / wire is used to define the output or input signal

//* implementing d flip flop module with different parameter 4 times *//

dff_r dff_0(.d_in(qn_0), .clik_in(clk_in), .rst_in(rst_in), .q(q_0), .q_n(qn_0));

dff_r dff_1(.d_in(qn_1), .clik_in(q_0), .rst_in(rst_in), .q(q_1), .q_n(qn_1));

dff_r dff_2(.d_in(qn_2), .clik_in(q_1), .rst_in(rst_in), .q(q_2), .q_n(qn_2));

dff_r dff_3(.d_in(qn_3), .clik_in(q_2), .rst_in(rst_in), .q(q_3), .q_n(qn_3));

assign o={qn_0, qn_1, qn_2, qn_3};

endmodulePositive Edge Triggered D flip flop Verilog Code

module pos_edge_df (q, d_in, clk_in, rst_in);

//* this module define d flip flop with q as output and data, clock and reset as input *//

input d_in, clk_in, rst_in; / input variable of the d flip flop is defined

output reg q; / output variable of the d flip flop is defined

always @ (posedge clk_in) / this block is implemented continuously with every positive edge of the clock pulse

if ( !rst_in) / if else statement

q<= 1’b0;

else

q<=d_in;

endmodule

Negative Edge Triggered D flip flop Verilog Code

module pos_edge_df (q, d_in, clk_in, rst_in);

//* this module define d flip flop with q as output and data, clock and reset as input *//

input d_in, clk_in, rst_in; / input variable of the d flip flop is defined

output reg q; / output variable of the d flip flop is defined

always @ (negedge clk_in) / this block is implemented continuously with every negative edge of the clock pulse

if ( !rst_in) / if else statement

q<= 1’b0;

else

q<=d_in;

endmoduleVerilog Code for D flip flop using Structural Model

/Structural model is used to integrate diffrenet blocks

module nand_gat(co, a, b); / this module defines NAND gate

input a, b;

output co;

assign co = ~( a & b);

endmodule

module not_gat(e, f); / this module defines NOT gate

input f;

output e;

assign e= ~f;

endmodule

module d_ff_strt(q,q_bar,d_in,clk_in); //* this module define d flip flop with q and qbar as output, and data and clock as input *//

input d_in, clk_in; / input variable of the d flip flop is defined

output q, q_bar; / output variable of the d flip flop is defined

not_gat not1 (d_bar, d_in); / here NOT gate module is implemented

/ next NAND gate module is implemented with different parameters 4 times

nand_gat nand1 (x, clk_in, d_in);

nand_gat nand2 (y, clk_in, d_bar);

nand_gat nand3 (q, q_bar, y);

nand_gat nand4 (q_bar, q, x);

endmoduleVerilog Code for Ring Counter using D flip flop

module dffc (q_in, d_in, clk_in); / d flip flop module is defined

output reg q_o;

input d_in,c_in;

initial

q_o=1'b1;

always@(posedge clk_in) / sensitivity is positive edge of the clock pulse

q_o = d_in;

endmodule

module ring_counterdff (q_o, clk_in); / ring counter module is defined with d flip flop

inout [3:0]q_o;

input clk_in;

/ d flip flop module is implemented with different parameters 4 times

dffc df1(q_o[0], q_o[3], clk_in);

dffc df2(q_o[1], q_o[0], clk_in);

dffc df3(q_o[2], q_o[1], clk_in);

dffc df4(q_o[3], q_o[2], clk_in);

endmoduleVerilog Code for T flip flop using D flip flop

module T_ff(q, t_in, clk_in, rst_in); / this module define T flip flop

input t_in, clk_in, rst_in; / input variable of the t flip flop is defined

output q; / output variable of the t flip flop is defined

always @ (posedge clk_in) / sensitivity of this block is positive edge of the clock pulse

if(rst_in)

t_in<=t_in^q;

endmoduleD flip flop Verilog Code with Testbench

//* following code is the test bench for a d flip flop is does not have any input or the output as variable, it's purposes is of exercising and verifying the functional correctness of the hardware model *//

module d_flipflopt_b;

reg d_in;

reg clk_in;

wire q;

d_flipflop_mod uut (.q(q),.d_in(d_in), .clk_in(clk_in) );

initial begin

d_in = 0;

clk_in = 0;

end

always #3 clk_in=~clk_in;

always #5 d_in=~d_in;

initial #100 $stop;

endmoduleMaster Slave D flip flop Verilog Code

module M_slave(d_in, reset_in,clk_in, q ,q_bar);/ this module define the master slave of d flip flop

input d_in, clk_in ,reset_in;

output q, q_bar;

Master Maste_r(d_in, reset_in, clk_in, qn, q_barn); / implementing master d flip flop module

Master Slav_e(q_n,reset_in,!clk_in,q, q_bar); / implementing slave d flip flop module

endmodule

module Master(d_in, reset_in, clk_in, q_in, q_bar); / this module defines d flip flop

input d_in, reset_in, clk_in;

output reg q, q_bar;

initial

q = 0;

always @(posedge clk_in) begin

if (~reset_in) begin

q <= d_in;

q_bar <= !d_in;

end

else begin

q <= 1'bx;

q_bar <= 1'bx;

end

end

endmoduleJK flip flop using D flip flop Verilog Code

module D_flip_flopf (input D_in ,clk_in ,Reset_in, enable_in, output reg Fo); / this module define D flip flop

always @(posedge clk_in) begin

if (Reset_in)

Fo <= 1'b0;

else if (enable)

Fo <= D_in;

end

endmodule

module JK_flip_flopf (input J_in, K_in ,clk_in, Reset_in, enable_in, output Q); / this module defines JK flip flop

wire S_1,S_2,S_3,S_4,S_5;

D_flip_flopf D1(S_4, clk_in, Reset_in,enable_in, Q );

not N2(S_5, Q);

and A1(S_1, J_in ,S_5);

not N1(S_3, K_in);

and A2(S_2,S_3,Q);

or O1(S_4,S_1,S_2);

endmoduleFrequency Divider using D flip flop Verilog Code

module freq_div_by2 (clk_out, clk_in, reset_in); //* this module defines frequency divider which can devide the frequency by 2 *//

input clk_in, reset_in;

output reg clk_out;

always @ (posedge clk_in)

if(reset_in)

clk_out<=0;

else clk_out<=~clk_out;

endmodule

D flip flop Verilog Code Gate Level

module dffgate(D_in, CLK_in, Q ,Q_n);

input D_in, CLK_in;

output Q, Q_n;

reg Q, Q_n, Ro, So;

always @(negedge CLK_in) begin

Ro = ~(~(~(D_in|So)|Ro)|CLK_in);

So = ~(~(D_in|So)|Ro|CLK_in);

Q = ~(Ro|Q_n);

Q_n = ~(So|Q);

end

endmoduleImage Credit : “Binary code” by Christiaan Colen is licensed under CC BY-SA 2.0

VHDL Code for D flip flop

library ieee;

use ieee.std_logic_1164.all;

entity d_flip_flop is

port (d_in, clk_in: in std_logic; q, q_bar: out std_logic);

end d_flip_flop;

architecture beh_v of d_flip _flop is

signal qn, q_barn: std_logic;

begin

Process (d_in, clk_in)

begin

If (clk_in’ event and clk_in = ‘1’)

then qn <=d_in;

end if;

End process;

q<=qn;

q_bar<=not (qn);

end beh_v;VHDL Code for D flip flop using Dataflow Modelling

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity d_flip_flop is

port (d_in, clk_in: in std_logic; q_in, q_out: inout std_logic);

end d_flip_flop;

architecture data_f of d_flip_flop is

signal d_1, s_1, r_1: std_logic;

begin

s_1 <= d_in nand clk_in;

d_1 <= d_in nand d_in;

r_1 <= d_1 nand clk_in;

q_in <= s_1 nand q_out;

q_out <= r_1 nand q_in;

end data_f;VHDL Code for D flip flop using Structural Model

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity d_f _f_st is

port (d_in, clk_in: in std_logic; q_in, q_out: inout std_logic);

end d_f_f_st;

architecture d_ff_s of d_f_f_st is

component nand_1

port (a, b : in std_logic; c : out std_logic);

begin

n_0: nand_1 port map(d_in, clk_in, s_1);

n_1: nand_1 port map(d_in, d_in, d_1);

n_2: nand_1 port map(d_1, clk_in, r_1);

n_3: nand_1 port map(s_1, q_out, q_in);

n_4: nand_1 port map(r_1, q_in, q_out);

end d_ff_s;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity nand_1 is

port (a, b: in std_logic; c: out std_logic);

end nand_1;

architecture beha_v of nand 1 is

begin

c<= a nand b;

end beha_v;D flip flop Behavioral VHDL code

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity d_flip_flop_bh is

port (d_in, clk_in, rst_in: in std_logic; q_in, q_out: out std_logic);

end d_flipflop_bh;

architecture beh_v of d_flip_flop_bh is

begin

process(d_in, clk_in, rst_in)

begin

If (rst_in = ‘1’) then q_in <= ‘0’;

else if (rising_edge(clk_in)) then q_in <= d_in;

q_out<= not d_in;

end if;

end process;

end beh_v;VHDL Code for D flip flop with Asynchronous Reset

library ieee;

use ieee.std_logic_1164.all;

entity d_ff_asy_rst is

port (d_in, clk_in, reset_in: in std_logic; q_out: out std_logic);

end d_ff_asy_rst;

architecture beha_v of d_ff_asy_rest is

begin

if (reset_in = ‘0’) then q_out<=’0’;

elseif (clk_in’ event and clk_in= ‘1’)

then

q_out<=d_in;

end if;

end process;

end beha_v;VHDL Code for D flip flop with Synchronous Reset

library ieee;

use ieee.std_logic_1164.all;

entity d_syn_reset

port( d_in, reset_in, clk_in: in std_logic; q_out: out std_logic);

end d_syn_reset;

architecture beha_v of d_syn_reset is

begin

process

begin

wait until (clk_in’ event and clk_in =’1’)

if reset_in = ‘0’ then q_out<=’0’;

else

q_out<= d_in;

end if;

end process;

end beha_v;VHDL Code for Negative Edge Triggered D flip flop

library ieee;

use ieee.std_logic_1164.all;

entity d_ff_neg is

port (d_in, clk_in: in std_logic; q_out: out std_logic);

end d_ff_neg;

architecture beha_v of d_ff_neg is

begin process (clk_in) begin

if (clk_in’ event and clk_in = ‘0’) then

q_out<= d_in;

end if;

end process;

end beha_v; Test Bench for D flip flop in VHDL

library ieee;

use ieee.std_logic_1164.all;

entity d_flip_flop_test is

end d_flip_flop_test;

architecture behaviour of d_flip_flop_test is

component d_flip_flop_test

port( d_in: in std_logic; clk_in : in std_logic; rst_in: in std_logic; d_out: out std_logic);

end component;

signal d_in: std_logic:= ‘0’;

signal clk_in : std_logic:= ‘0’;

signal rst_in: std_logic:= ‘1’;

signal d_out: std_logic;

constant clk_p: time:=20ns;

begin

uut: d_flip_flop_test

port map(d_in=>d_in; clk_in => clk_in; rst_in=> rst_in; d_out=> d_out);

clk_p: process begin

clk_in<=10;

wait for clk_p/2;

clk_in<=’1’;

wait for clk_p/2;

end process;

sti_prc: process

begin

rst_in<=’1’;

wait for 50 ns;

rst_in<= ‘0’;

d_in <= ‘0’;

wait for 50ns;

rst_in<=’0’;

d_in<= ‘1’;

wait;

end process;

end;4 bit Shift Register using D flip flop VHDL Code

library ieee;

use ieee.std_logic_1164.all;

entity p_I_p_o is

port(

Clk_in: in std_logic;

D_in: in std_logic_vector(3 downto 0);

Q_1: out std_logic_vector(3 downto 0)

);

end p_I_p_o;

architecture archi of p_I_p_o is

begin

process (clk)

begin

if (CLK_in'event and CLK_in='1') then

Q_1 <= D_in;

end if;

end process;

end archi;VHDL Code for 8 bit Register using D flip flop

library ieee;

use ieee.std_logic_1164.all;

entity reg_sip_o is

port (clk_in, clear : in std_logic; input_d : in std_logic; q: out std_logic vector (7 downto 0 ) );

end reg_sip_o;

architecture arch of reg_sip_o is

begin

process (clk_in)

If clear = ‘1’ then

q<= “00000000”;

elseif (clk_in’ event and clk_in = ’1’ ) then

q(7 downto 1)<= q(2 downto 0);

q(0)<= input_d;

end if;

end process;

end arch;VHDL Code for Asynchronous Counter using D flip flop

//*following is the VHDl code for a asynchoronous counter designed with d flip flop *//

library ieee;

use ieee.std_logic_1164.all;

entity dff1 is

port (d_in, clk_in ,clr_in : in std_logic; q, q_bar : inout std_logic);

end dff1;

architecture my_dffbharch of dffl is

begin

process (d_in, clk_in, clr_in)

begin

if (clr_in = '1') then

if (clk_in = '1') AND (clk_in'EVENT) then

q <= d_in;

q_bar <= not (d_in);

end if;

else

q <= '0';

q_bar <= '1';

end if;

end process;

end my_dffbharch;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity dcoun is

port(clk_in, clr_in :in std_logic;

q, q_b:inout std_logic_vector(3 downto 0));

end dcoun;

architecture arch of dcoun is

component dff1 is

port(d_in, clk_in, clr_in :in std_logic;

qi, q_bar:out std_logic);

end component;

signal k ,p , m :std_logic;

begin

k<=qi (0);

p<=qi (1);

m<=qi (2);

a1:dff1 port map('1','1', rst_in, clk_in , qi(0),q_b(0));

a2:dff1 port map('1','1', rst_in,k,q(1),q_b(1));

a3:dff1 port map('1','1', rst_in, p, qi(2), q_b(2));

a4:dff1 port map('1','1', rst_in, m,qi(3), q_b(3));

end arch;I have graduated in Applied Electronics and Instrumentation Engineering. I’m a curious-minded person. I have an interest and expertise in subjects like Transducer, Industrial Instrumentation, Electronics, etc. I love to learn about scientific researches and inventions, and I believe that my knowledge in this field will contribute to my future endeavors.