Edge triggering in flip flops is a crucial concept in digital electronics. It refers to the mechanism by which a flip flop changes its state based on the transition of a specific input signal. Unlike level triggering, which responds to the continuous value of the input signal, edge triggering focuses on the rising or falling edge of the signal. When the input signal transitions from low to high or high to low, the flip flop captures and stores the current state. This mechanism ensures that the flip flop only responds to the specific edge of the input signal, providing stability and reliability in digital circuits.

Key Takeaways

| Edge Triggering in Flip Flops |

|---|

| – Responds to the rising or falling edge of the input signal |

| – Captures and stores the current state of the flip flop |

| – Provides stability and reliability in digital circuits |

Understanding Flip Flops in Electronics

Definition and Meaning of Flip Flops

Flip flops are fundamental building blocks in digital electronics that are used for storing and manipulating binary information. They are sequential logic circuits that can store one bit of data, which can be either a 0 or a 1. Flip flops are widely used in various electronic devices, such as computers, calculators, and communication systems.

The Role of Flip Flops in Digital Electronics

Flip flops play a crucial role in the operation of digital electronics. They are used to store and transfer data, synchronize signals, and control the timing of various operations. Understanding the operation and functionality of flip flops is essential for designing and analyzing digital circuits.

Flip Flop Operation

The operation of a flip flop is based on its ability to latch and store a binary state. It can hold this state until it is changed by an external input or a clock signal. Flip flops can be triggered by either the rising edge or the falling edge of a clock signal, which is known as edge triggering. This allows for precise control over the timing and synchronization of digital circuits.

Flip Flop Functionality

The functionality of a flip flop is determined by its internal circuitry and the inputs it receives. The most common types of flip flops include the D flip flop, JK flip flop, SR flip flop, and T flip flop. Each type has its own unique characteristics and applications. For example, the D flip flop is commonly used for data storage, while the JK flip flop is used for toggling and counting operations.

Flip Flop Timing

Timing is a critical aspect of flip flop operation. It refers to the precise control and synchronization of signals within a digital circuit. Flip flops have specific timing requirements, such as setup time, hold time, and propagation delay. These parameters ensure that the inputs and outputs of the flip flop are stable and reliable.

Flip Flop Circuit Design

Designing a flip flop circuit involves selecting the appropriate type of flip flop and configuring its inputs and outputs. The circuit design must take into account factors such as power consumption, speed, and noise immunity. Flip flop circuits can be implemented using various electronic components, such as transistors, gates, and logic gates.

Flip Flop State and Transition

The state of a flip flop refers to the binary value it is currently storing. It can be either a 0 or a 1. Flip flops can transition from one state to another based on the inputs they receive. These transitions can occur on the rising or falling edge of a clock signal, depending on the type of flip flop and its triggering mechanism.

Flip Flop Latch and Storage

A flip flop can latch and store a binary state until it is changed by an external input or a clock signal. This ability to store data is essential for the operation of digital circuits. Flip flops can be used to store temporary data, perform calculations, and synchronize signals within a system.

Flip Flop Delay and Propagation Delay

Flip flops have a certain delay associated with their operation, known as propagation delay. This delay is the time it takes for the output of the flip flop to change in response to a change in its inputs. It is important to consider the propagation delay when designing digital circuits to ensure proper timing and synchronization.

Flip Flop Setup Time and Hold Time

Setup time and hold time are critical parameters in flip flop operation. Setup time refers to the minimum amount of time that the input signal must be stable before the clock signal changes. Hold time refers to the minimum amount of time that the input signal must remain stable after the clock signal changes. Violating these timing requirements can lead to errors and unreliable operation.

Flip Flop Race Condition and Metastability

Race conditions and metastability are potential issues that can occur in flip flop circuits. A race condition occurs when the outputs of a flip flop change unpredictably due to timing differences in the inputs. Metastability refers to a temporary state of a flip flop where it is unable to settle into a stable state. These issues can lead to incorrect data storage and unreliable operation of digital circuits.

The Concept of Edge Triggering

Definition of Edge Triggering

In the world of digital electronics, edge triggering is a fundamental concept that plays a crucial role in the operation of flip flops. A flip flop is a circuit element that can store and manipulate binary information. It is widely used in digital systems for various purposes such as data storage, synchronization, and sequential logic.

Edge triggering refers to the mechanism by which a flip flop responds to a specific transition on its clock input. Instead of being sensitive to the level of the clock signal, a flip flop is triggered by a change in the clock signal from one logic level to another. This change can be either from low to high (rising edge) or from high to low (falling edge).

The triggering edge determines when the flip flop captures and stores the input data. It is an essential aspect of flip flop functionality, as it allows for precise control over the timing and synchronization of data within a digital system.

The Importance of Edge Triggering in Flip Flops

Edge triggering is of paramount importance in the design and operation of flip flops. It enables the flip flop to latch and store the input data at the desired moment, ensuring accurate and reliable operation.

One key advantage of edge triggering is its ability to eliminate the issues associated with level triggering. In level triggering, the flip flop continuously monitors the level of the clock signal, which can lead to instability and unpredictable behavior. Edge triggering, on the other hand, provides a well-defined and controlled transition point for capturing the input data, minimizing the chances of errors and glitches.

The timing characteristics of edge triggering, such as setup time and hold time, are critical for proper flip flop operation. The setup time refers to the minimum time interval before the clock edge at which the input data must be stable for reliable capture. The hold time, on the other hand, is the minimum time interval after the clock edge during which the input data must remain stable.

By carefully designing the flip flop circuit and considering the timing requirements, edge triggering ensures that the input data is correctly captured and stored, avoiding any race conditions or metastability issues. It provides a robust and predictable mechanism for storing and transferring binary information within a digital system.

The Operation of Edge-Triggered Flip Flops

Edge-triggered flip flops are essential components in digital circuits, used for storing and manipulating binary data. They are widely employed in various applications, ranging from memory elements to sequential logic circuits. In this section, we will explore the mechanism and functionality of two types of edge-triggered flip flops: the D flip-flop and the T flip-flop.

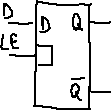

The Mechanism of Edge-Triggered D Flip-Flop

The D flip-flop is a fundamental building block in digital circuit design. It consists of two stable states, commonly referred to as “0” and “1”. The flip-flop’s output state is determined by the input signal and the clock signal. The clock signal acts as a control mechanism, allowing the flip-flop to transition from one state to another only when a specific edge of the clock signal is detected.

The D flip-flop operates based on the following mechanism:

1. When the clock signal transitions from low to high (rising edge), the input signal (D) is sampled and stored in the flip-flop.

2. The stored value is then propagated to the output (Q) of the flip-flop.

3. When the clock signal transitions from high to low (falling edge), the input signal is ignored, and the output remains unchanged.

This edge-triggered behavior ensures that the output of the D flip-flop only changes when the clock signal transitions, providing synchronization and stability to the circuit. The D flip-flop is widely used in applications that require precise timing and control, such as data storage and synchronization circuits.

The Functionality of Edge-Triggered T Flip-Flop

The T flip-flop, also known as the toggle flip-flop, is another type of edge-triggered flip-flop. It has a single input (T) and a single output (Q). The T flip-flop‘s output toggles between its two stable states (0 and 1) with each rising edge of the clock signal, depending on the input value.

The functionality of the T flip-flop can be summarized as follows:

1. When the clock signal transitions from low to high (rising edge), the input signal (T) is sampled.

2. If the input signal is high (1), the output toggles to the opposite state. If the input signal is low (0), the output remains unchanged.

3. When the clock signal transitions from high to low (falling edge), the input signal is ignored, and the output remains unchanged.

The T flip-flop is commonly used in applications that require frequency division, counting, or generating periodic waveforms. Its ability to toggle between states based on the clock signal makes it a versatile component in digital circuit design.

Why Edge Triggering is Preferred in Flip Flops

Edge triggering is a popular method used in flip flops for various reasons. It offers several advantages over level triggering, making it the preferred choice in many flip flop designs. In this section, we will explore the advantages of edge triggering over level triggering and discuss the practical applications of edge triggering in flip flops.

The Advantages of Edge Triggering Over Level Triggering

Improved Timing Control: Edge triggering allows for precise timing control in flip flops. By triggering the flip flop on the rising or falling edge of the clock signal, it ensures that the flip flop transitions at the desired moment. This is particularly important in applications where accurate timing is crucial, such as in synchronous digital systems.

Reduced Power Consumption: Edge triggering helps in reducing power consumption in flip flops. Since the flip flop changes its state only during the transition of the clock signal, it consumes less power compared to level triggering, where the flip flop constantly monitors the input signal. This makes edge-triggered flip flops more energy-efficient, which is advantageous in battery-powered devices or low-power applications.

Elimination of Race Conditions: Edge triggering eliminates the possibility of race conditions in flip flops. A race condition occurs when the output of a flip flop changes unpredictably due to timing differences between the input signals. By triggering the flip flop on the edge of the clock signal, it ensures that the input signals are stable and avoids any race condition issues.

Mitigation of Metastability: Edge triggering helps in mitigating the effects of metastability in flip flops. Metastability is a temporary state that occurs when the input signal to a flip flop is changing near the edge of the clock signal. This can lead to unpredictable outputs and can cause system failures. By using edge triggering, the flip flop provides a stable setup time for the input signal, reducing the chances of metastability.

The Practical Applications of Edge Triggering in Flip Flops

Edge triggering finds wide applications in various flip flop circuits and designs. Some of the practical applications of edge triggering in flip flops include:

Memory Storage: Edge-triggered flip flops are commonly used as memory storage elements in digital systems. They can store binary information and retain it until the next clock edge triggers a state transition. This makes them suitable for applications such as registers, counters, and memory units.

Synchronization: Edge-triggered flip flops are essential for synchronizing signals in digital systems. They ensure that signals are sampled and processed at the desired moments, enabling proper synchronization between different parts of the system. This is crucial in applications such as data communication, where accurate synchronization is necessary for reliable data transmission.

State Machines: Edge-triggered flip flops play a vital role in the implementation of state machines. State machines are widely used in digital systems for controlling sequential operations. By using edge-triggered flip flops, the state transitions can be precisely controlled, allowing for efficient and reliable operation of the state machine.

How does edge triggering in flip-flops operate and what is the difference between a latch and a flip-flop?

The concept of edge triggering in flip-flops involves the ability of a flip-flop to change its state only at specific times, determined by the rising or falling edge of a clock signal. This operation enables the synchronization of data transfer within digital circuits. However, it is important to understand the difference between a latch and a flip-flop. The term “Difference between latch and flip-flop” refers to the distinction between these two circuit elements, which although similar, have some fundamental differences. A latch is level-sensitive, meaning it continuously checks for input changes and retains its output as long as the enable input is active. On the other hand, a flip-flop is edge-triggered, meaning it changes its output only at specific clock edges. To gain further insight into the comparison of a latch and a flip-flop, visit Difference between latch and flip-flop.

Frequently Asked Questions

Q1: What is the meaning of a flip-flop?

A1: A flip-flop is a fundamental building block in digital electronics used for storing binary information. It can store one bit of data and has two stable states, typically labeled as “0” and “1”.

Q2: What is the functionality of a flip-flop circuit?

A2: A flip-flop circuit can store and remember binary information, allowing it to retain its state until a new input triggers a change. It is commonly used for sequential logic and memory elements in digital systems.

Q3: Why is edge triggering preferred in flip-flops?

A3: Edge triggering in flip-flops ensures that the output changes only when there is a transition on the clock signal’s rising or falling edge. This helps in synchronizing and controlling the timing of the flip-flop operation.

Q4: What is the difference between an edge-triggered flip-flop and a latch?

A4: An edge-triggered flip-flop changes its output state only on the rising or falling edge of the clock signal, while a latch can change its output state at any time, depending on the input. Flip-flops are more suitable for sequential circuits, whereas latches are commonly used in combinational circuits.

Q5: What is the purpose of flip-flop timing parameters like setup time and hold time?

A5: Flip-flop timing parameters, such as setup time and hold time, ensure that the input signals are stable and meet the required timing conditions before and after the clock edge. These parameters prevent potential errors and race conditions in the flip-flop operation.

Q6: What is the meaning of the term “metastability” in flip-flops?

A6: Metastability refers to an unstable state that can occur in a flip-flop when the input signal transitions near the clock edge. It can result in unpredictable output values and is a potential issue in high-speed digital systems.

Q7: How does a flip-flop store data?

A7: A flip-flop stores data by using feedback from its output to its input. The output state is latched and remains stable until a triggering event, such as an edge on the clock signal, causes the flip-flop to transition to a new state.

Q8: What is the role of a clock signal in flip-flop operation?

A8: The clock signal in a flip-flop provides the timing reference for when the input data should be sampled and when the output should change. It synchronizes the operation of the flip-flop and ensures proper functionality.

Q9: What is the propagation delay of a flip-flop?

A9: The propagation delay of a flip-flop is the time it takes for the output to change after a valid input transition occurs. It is an important parameter that affects the timing and performance of digital circuits.

Q10: How can flip-flops be used in electronic circuits?

A10: Flip-flops are widely used in electronic circuits for various applications, including memory elements, counters, shift registers, and state machines. They provide a means of storing and manipulating binary information in digital systems.

Also Read:

- Can an hpf be used as a differentiator under certain conditions

- Why is miniaturization a challenge in flip flop designs

- Where are fourier and laplace transforms used in the study of signals

- Can a zener diode recover after experiencing a transient voltage spike

- Is there a specific direction for current flow in a diode

- Power vs voltage

- Why are feedback loops essential in flip flops

- Does filtering a signal affect its frequency spectrum

- Is there a hierarchy in flip flop versatility

- What is a flip flop circuit

The TechieScience Core SME Team is a group of experienced subject matter experts from diverse scientific and technical fields including Physics, Chemistry, Technology,Electronics & Electrical Engineering, Automotive, Mechanical Engineering. Our team collaborates to create high-quality, well-researched articles on a wide range of science and technology topics for the TechieScience.com website.

All Our Senior SME are having more than 7 Years of experience in the respective fields . They are either Working Industry Professionals or assocaited With different Universities. Refer Our Authors Page to get to know About our Core SMEs.